基于国产银河飞腾多核 DSP +FPGA的图像识别硬件设计与算法实现

随着监测卫星的发展,如何快速对卫星图像中的目标物进行识别成为关键技

术。为了实现星载关键器件的国产化,并为整个系统提供更高的性能和更好的实

时性,本课题将以国防科技大学计算机学院自主研发的高性能多核 DSP 芯片作为

处理核心,辅以 FPGA,搭建图像采集和识别硬件处理平台,并在该平台上研究和

实现舰船目标识别算法。

主要工作:①设计基于飞腾多核 DSP+FPGA 的处理框架。该框架充

分利用了 DSP 处理数字信号的能力以及 FPGA 控制接口的能力,结构灵活,且满

足体积小、功耗低、处理速度快的设计要求。②完成整个平台的硬件电路设计。

③完成各功能模块的调试。FPGA 能够实现图像的采集和显示,从采集到的信息中

提取出有效图像数据并对图像进行灰度化处理,且与 DSP 实现数据传输和通信。

DSP 能够实现与主控计算机的通信。④采用基于灰度阈值算法和基于有效边缘信

息的算法识别出舰船目标,找出目标物在图像中的相对位置并将处理结果显示在

显示设备上。⑤根据飞腾多核 DSP 的特点对程序进行多核优化,提高程序的效率。

设计出的硬件平台能够实现图像的采集与处理,识别出一般情况下的舰船目

标并将结果显示在显示设备上。

由国防科技大学计算机学院微电子所自主研发的高性能多核处理器 FT-XXX,

在同等工作频率下,其数字信号处理能力比通用微处理器高 1~2 个数量级,功耗

则低 1~2 个数量级。在现代化战争中,需要及时对获取的重要信息进行处理和分

析。因此,飞腾 DSP 以其强劲的数字信号处理能力而得到广泛应用,范围涉及精

确制导、雷达信号处理、保密通信、飞行控制、电子干扰和声呐探测等应用邻域,

是信息处理系统研制中需要最迫切的核心器件之一。

如今,银河飞腾 DSP 已经应用到多个领域。比如无人飞机的图像拍摄及处理、

火炮系统的控制装置、水下信息处理系统等。将飞腾多核 DSP 应用于卫星上还属

首次。研究星上图像采集与识别平台将拓宽银河飞腾 DSP 的应用领域,获取飞腾

芯片在真实太空环境中的工作状态与工作能力,为太空环境下的系统级设计积累

经验,并检验飞腾芯片在实际应用中能否达到设计要求。

同时,研究飞腾多核 DSP 在卫星上的应用有利于实现卫星核心器件国产化,

对信息安全具有重要意义。

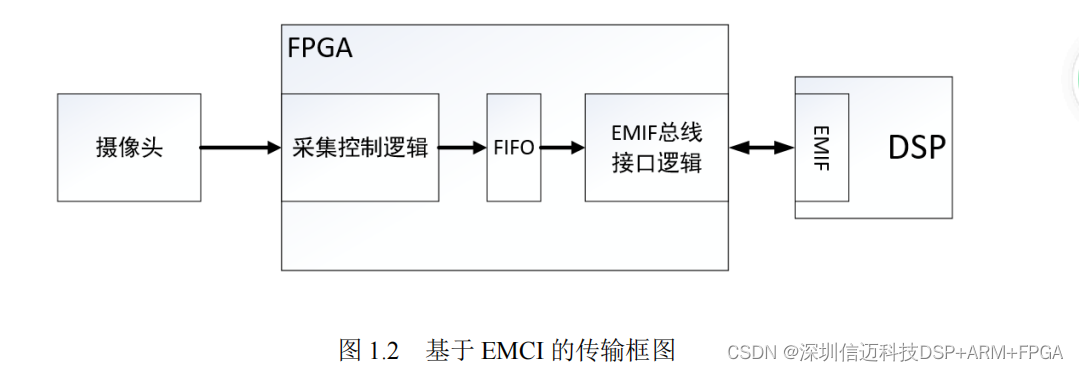

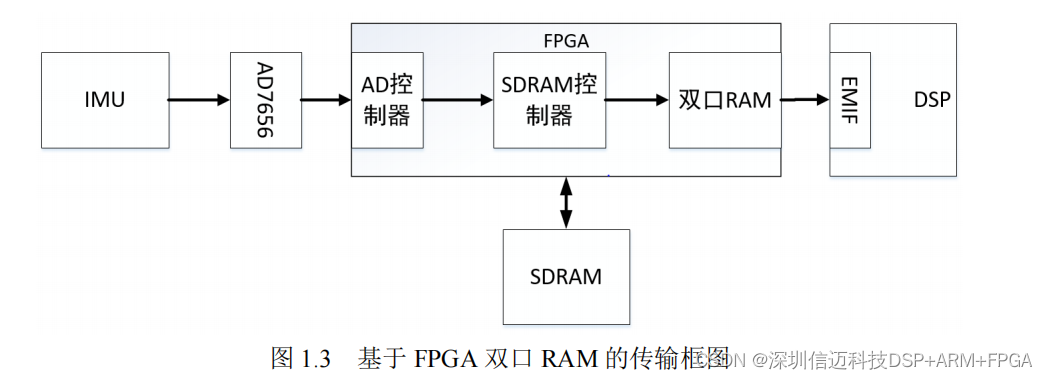

嵌入式捷联导航系统[5],其框图如图 1.3 所示。此设计中,FPGA 将采集到的

图像数据经过初步处理后存入 SDRAM,同时又将数据存入双口 RAM 中。双口

RAM 速度快、实时性强。且容易操作,DSP 通过 EMIF 来实现对双口 RAM 中数

据的读取。这样的设计不仅能够存储多帧图像,且能够满足 DSP 与 FPGA 之间的

快速数据传输,不足的是要选用具有足够存储器资源的 FPGA 型号。

FPGA+DSP 的图像处理结构[6,7]使得图像处理平台变得更加便携、功耗更低、

性能更强,该结构不停地得到发展和优化[8,9]。本文结合了飞腾 DSP 的特点,且以

能够搭载上天为目标,设计了性能更加强大且稳定性强的图像处理硬件平台,同

时加以实现与完善。

硬件电路原理设计

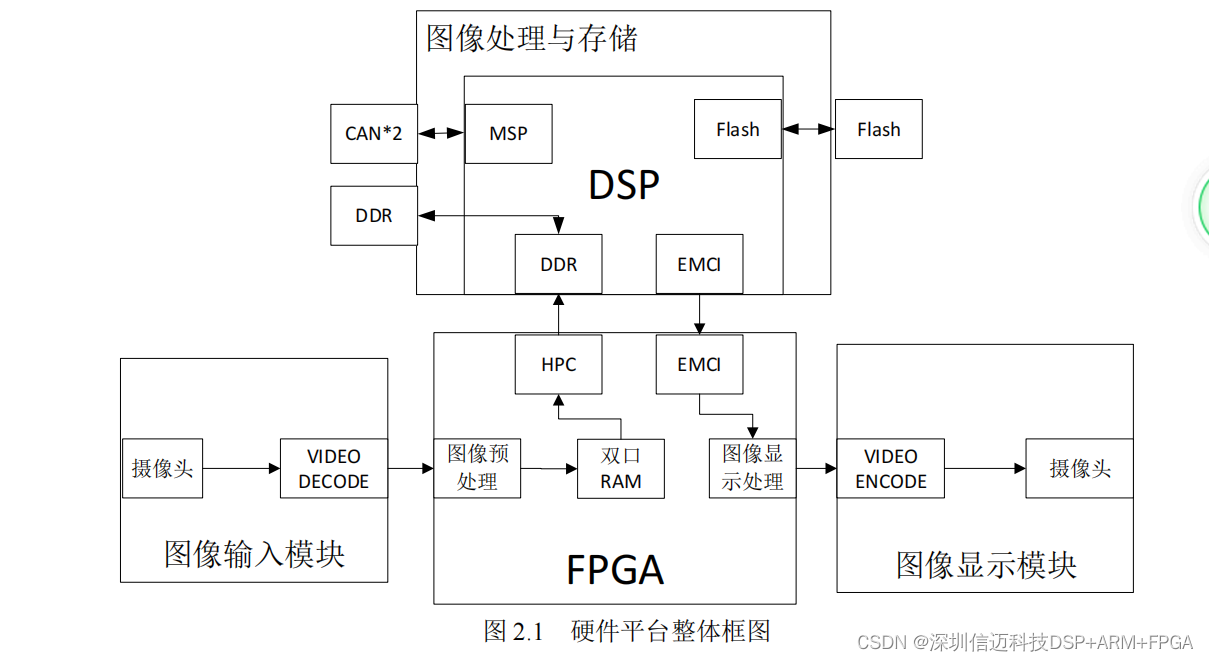

基于飞腾多核 DSP+FPGA 的图像处理平台如图 2.1 所示,该平台主要包括 4

个主要模块,图像输入模块、图像预处理模块、图像处理和存储模块和图像显示

模块。图 2.1 显示了课题实际应用中使用到的接口,而在整个板卡的设计中还预留

了其它的一些功能接口,包括 FPGA 部分预留了硬盘存储接口可以存储接收到的

原始图像,FPGA 与 DSP 进行通信除了 HPC 总线和 EMCI 总线外还预留了 SRIO

接口,这在后面的章节将进行详细的介绍。本文将分别介绍各个模块的工作原理

与实现,以及整个系统的工作流程和效果。

如图 2.1 所示的整体框图,摄像头采集图像,然后经过 A/D 转换芯片将视频

信号转换为 BT.656 格式的数字信号,图像数字信号进入 FPGA 以后首先将 BT.655

格式的图像进行去除消隐信号的操作,只保留有效数据,并将有效数据拼接成完

整的一幅图。FPGA 将图像数据存入 RAM 中,FPGA 内部通过硬件语言实现 HPC

接口逻辑,与 DSP 的 HPC 接口连接,通过 HPC 总线协议将数据传送到 DSP 的

DDR2 空间。DSP 在接收图像数据前需要配置 DDR2,使其能够正常工作。DSP

对图像进行处理,通过识别算法找出舰船目标,确定出舰船在图像中的相对坐标,

然后将坐标信息通过 EMCI 传输给 FPGA。FPGA 得到坐标信息后,结合原始图像,

然后将图像信息传输给视频解码芯片,接着在输出显示设备上显示原始图像和舰

船相对位置的十字丝。同时,DSP 通过 Mfsp 与 CAN 芯片进行通信,CAN 芯片通

过 CAN 总线与卫星进行通信。

整体的硬件设计框架

在确定整体的硬件平台是 FPGA+DSP 的结构后,就要对整个硬件平台进行详

细的设计。设计目标是要搭载到卫星上的舰船目标识别系统,所以在设计过程中

首先要考虑到的是系统的稳定性、在稳定的前提下提高系统的性能,降低整体的

功耗。

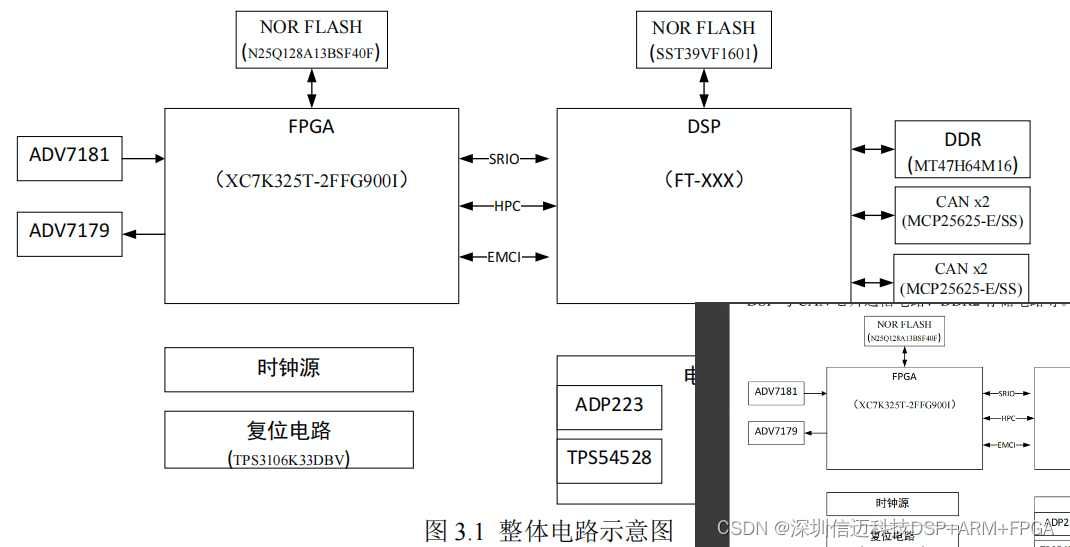

在设计整个硬件平台中,可以将整个硬件电路分为下面几个部分:时钟电路、

电源电路、复位电路、图像采集电路、图像显示电路、DSP 与 FPGA 通信电路、

DSP 与 CAN 芯片通信电路、DDR2 存储电路等。电路示意图如图 3.1 所示。

DSP 选用的是由国防科大计算机学院微电子所自主研制的数字信号处理芯片

FT-XXX,该款 DSP 数字处理能力强劲,拥有 4 个 DSP 核和一个 RISC 核、工作

频率最高达到 500MHz。其应用范围广泛,涉及到雷达信号处理、电子对抗、声呐

检测、图像处理等多个领域。

FPGA(现场可编程逻辑器件)选用的是 Xilinx 公司的 XC7K325T-2FFG900I,

虽然与 CPLD(复杂逻辑可编程器件)相比速度有所不及,但是其能够提供更多的

逻辑资源。该款 FPGA 是 Xilinx 主打的低功耗系列 FPGA 中的一款,共有 25475

个 LAB/CLB,326080 个逻辑单元,16404480 位数 RAM。其性能与容量能够轻松满

足图像处理平台对图像数据进行搬移、转换、缓存的任务。

飞腾多核 DSP 支持多种外围总线接口,包括高速 SRIO、GPIO、EMCI、HPC

等。考虑到图像处理板的需要传输数据量巨大且要保证该处理板具有较好的扩展

性,所以在设计过程中采用 3 种方式来进行 FPGA 与 DSP 之间的数据传输,分别

为 SRIO、EMCI 和 HPC。

图像采集与解码采用的 ADI 公司生产的 ADV7181B 芯片,该芯片能够自动检

测输入的是哪种标准制式的视频信号并进行解码,输出数字格式 8 位或 16 位的

ITU-R BT.656 YCbCr 4:2:2 的图像数据,同时还输出场同步信号 Field、水平同步

信号 Hs、垂直同步信号 Vs。在开发过程中可以通过判断 Field、Hs、Vs 的值来对

数据进行处理,获得完整的一副图片。

图像显示部分,图像的编码采用的是 ADI 公司的 ADV7179 芯片,该芯片能

够对 BT.656 格式进行编码,通过 DAC0~DAC2 共 3 个端口输出信号。

外围存储器件选用的是 4 片 MT47H64M16,组成 512MB 存储空间,位宽为 64

位,带宽达到 3.2GB/S。飞腾 DSP 兼容标准的 DDR2 协议,能够完美地支持 DDR2

器件