ZYNQ+AD8285高速毫米波雷达数据采集系统设计

传统的毫米波雷达采用DSP+FPGA的处理模 块,通过FPGA增加采集数据吞吐能力,通过DSP

器件完成数据处理算法。为满足如今毫米波雷达 低功耗小型化的指标要求,同时保证数据接口的

稳定性和速度,本设计提出一种基于Xilinx公司的ZYNQ采集系统,具有高集成度,高可靠性的特

点。其中PL端逻辑资源可以控制高速的AD数据采 集。PS端将采集数据传输至上位机,通过Matlab平 台对采集系统进行动态参数分析,实验表明AD各 项动态参数达到设计要求,验证了该高速采集系统 设计的合理性。

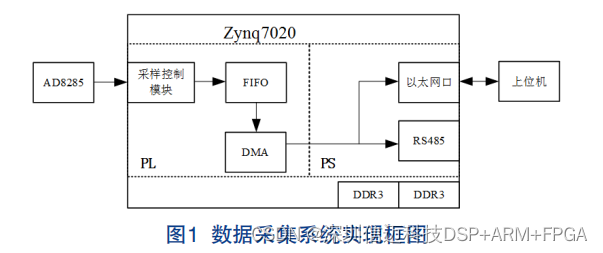

1 系统总体设计

在毫米波雷达应用中,数据采集系统的实现主 要由以下部分组成:ADI公司的12bit的AD8285,

在Xilinx xc7z020clg400-2 PL端的采样控制模块 FIFO和DMA IP核,PS端以太网口和RS485以及上

位机。图1为数据采集系统实现框图。

2 AD转换模块介绍

AD8285是一款低成本低功耗的四通道,12位 精度高速模数转换器。各通道具有16 dB至34dB的

增益范围,ADC转换速率最高可达72Msps,每个通道185mW(12bit和72Msps时)。本次设计中使用外部40MHz晶振通过ZYNQ内部PL端的PLL锁相环产生差分时钟驱动AD8285。AD8285通过SPI接口配置功能寄存器,SPI串行时钟设置为5Mhz,部分引脚说明如表1所示。

在PL端使用自顶向下的方法,使用verilog语言设 计AD的驱动电路;分别是采样控制模块,寄存器功 能配置模块,三线制SPI接口模块。采样控制模块负责AD8285与控制前端发射芯片的同 步采样功能,寄存器功能配置模块通过SPI接口向地址写数据实现对多个寄存器的读写。三线制SPI接口模块 是一种高速,全双工的通信总线,由串行时钟(SCLK)、串行数据输入 /输出(SDIO)、片选信号(CSN)组成。在指令周期传输中前16bit,其中R/W是读写指示位、W1和W0控制

传输的字节数,传输的后8bit代表了 寄存器的地址;数据周期会写入8bit 需要写入寄存器的值[1,2]。三线制SPI 时序如图2所示。

3 采样流程控制

在毫米波雷达应用中,通过 AD8285采集雷达 多普勒回波数据,利用AXI总线通过ZYNQ器件中

PL与PS的通信,经PL端DMA IP核将数据传输到 PS 端的DDR3,根据数据流向,DMA IP核在设置时选 择只使用写通道,其他保持默认选项。PS端使用 LWIP使用千兆以太网口将采集数据发送到PC端对数 据进行处理。PL每次发完一帧回波数据,DMA IP核 产生一个中断信号,PS得到中断信号后将DDR3缓 存的数据通过乒乓操作由TCP协议发送到PC。同时 系统中扩展了RS485串口可以打印调试信息,最后 使用Flash固化测试程序[3]。

4 测试结果仿真分析

ADI公司提供了AD8285灵活的输出测试模式, 利用vivado2017.3ILA逻辑分析仪进行测试,先以

棋盘形式输出101010101010以验证SPI接口通信。 然后,测试多通道与数据的对应关系,PGA增益调 节,并分析多个通道之间相位差。测试时使用外部 的信号发生器作为AD8285采集模块的输入,信号发 生器上位机可设置4通道同时输入正弦波信号,可通 过SPI接口配置AD8285转换率,增益以及截止频率 等功能。

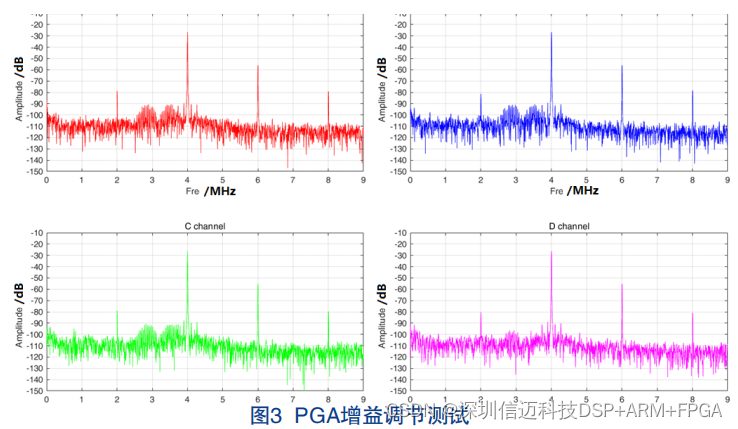

4.1 PGA增益调节测试

AD转换率设置为72Msps,4个通道加同一路信 号4Mhz正弦波信号,每个通道的输入信号幅度和

相位一致,信号幅度满幅输入,每个通道采集4096 个点并存储。用Matlab对每个通道的4 096个点做 FFT,记录频谱曲线,如图3所示。

4.2 相位差测试

外部信号发生器同时给四个通道输入4路1MHz的模拟信号,四个通道相位全部设置0分析相位差。

在72Msps转换率的情况下,相邻两个采样点的时间 间隔约为13.8ns,对1MHz的信号来说对应的相位差 是5º。经Matlab分析相位符合预期,如表2所示。