【国产虚拟仪器】基于FPGA+JESD204B 时钟双通道 6.4GSPS 高速数据采集模块设计(一)总体方案

本章将根据高速数据采集指标要求,分析并确定高速数据采集模块的设计方

案,由此分析数据存储需求及存储速度需求给出高速大容量数据存储方案,完成

双通道高速数据采集模块总体设计方案,并综合采集、存储方案及 AXIe 接口需求

给出逻辑器件选型。

2.1 高速数据采集模块指标及方案分析

2.1.1 高速数据采集指标

本文基于 AXIe 测试总线平台的高速数据采集模块主要技术指标如下:

1)最大采样率:6.4GSPS

2)ADC 分辨率:12bits

3)通道数:2

4)模拟输入带宽:1GHz

5)耦合:DC

6)输入信号幅值:125mV、250mV、500 mV、1V

7)信噪比:54dB@380MHz

8)存储深度:2Gpts

9)传输:支持 AXIe 规范中 PCIe 2.0 版本四通道、5.0Gbps 的接口协议

10)触发及同步:支持标准 AXIe 总线的触发、同步功能

2.1.2 高速数据采集方案

数据采集模块首先需实现模拟信号的数字化,其后才能对数字化信号进行缓

存、滤波及传输等处理。ADC 作为数据采集模块的关键器件,其性能指标影响着

整个采集模块的性能。当 ADC 采样率较低时,可采用等效采样技术与时间交替采

样技术实现高采样率的数据采集[13]。等效采样技术主要针对重复性的周期信号,

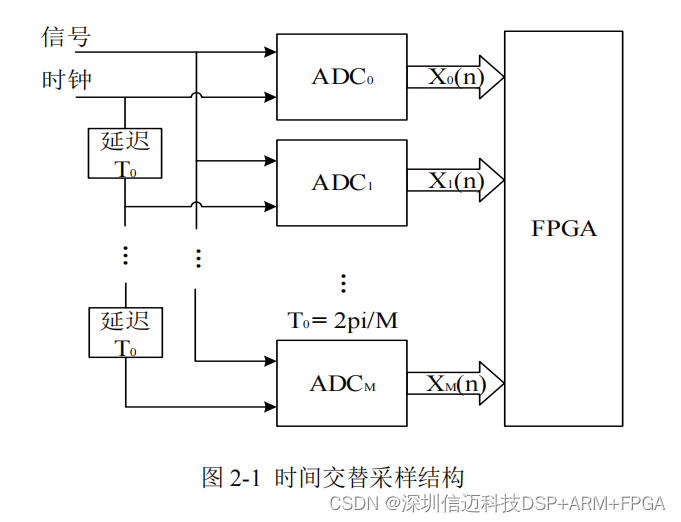

具有局限性;而时间交替采样技术对信号没有限制,应用更为广泛。时间交替采

样结构如图 2-1 所示,多个 ADC 同时采样同一信号,各 ADC 的采样时钟以固定

相位差驱动对应 ADC,采样数据在后端接收器件中按时间顺序拼合。通过时间交

替采样,采集系统的采样率将提高至多个 ADC 采样率之和。

根据该采集模块的采样率及分辨率指标,在 TI 及 ADI 公司官网以采样率

3.2GSPS 或 6.4GSPS 及分辨率 12bits 为关键信息筛选出两款 ADC 芯片,分别为

ADC12D1600、ADC12DJ3200。ADC12D1600 最高采样率为 3.2GSPS,分辨率为

12bits,ADC12DJ3200 最高采样率为 6.4GSPS,分辨率为 12bits。其中 ADC12D1600

在时间交替采样的情况下也能达到 6.4GSPS 的采样率,因此 ADC12D1600 及

ADC12DJ3200 在采样率及分辨率上都能满足采集模块的指标要求。下文将讨论这

两款芯片实现 6.4GSPS 数据采集的方案。

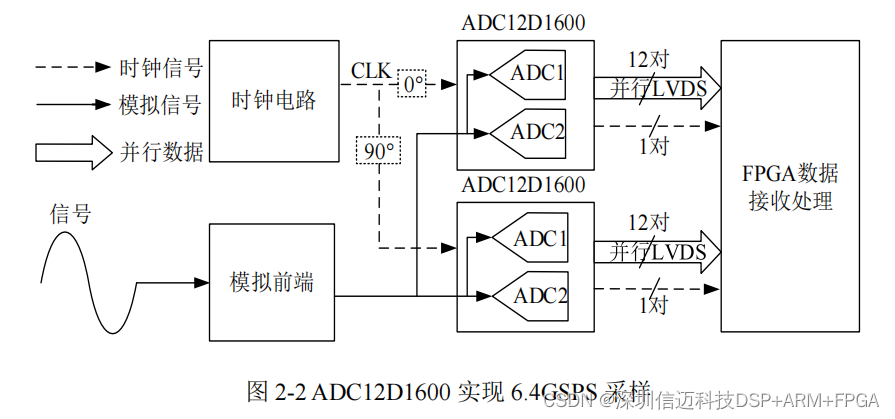

ADC12D1600 内部集成了两个 ADC 内核,有两种工作模式,一个是单沿采样

模式,另一个是双沿采样模式[14]。单沿采样模式时,两个 ADC 内核在时钟上升沿

分别采样对应通道输入信号,最高采样率为 1.6GSPS;双沿采样模式时,两个 ADC

内核分别在时钟上升沿及下降沿采样采样同一通道输入信号,最高采样率为

3.2GSPS。ADC12D1600 的数据输出采用 LVDS 并行接口,一位数据位采用一对

LVDS 差分线,则 ADC12D1600 需要 12 对数据线。LVDS 并行接口还需要同步时

钟信号,即一对时钟差分线用于 FPGA 内部同步接收并处理采样数据。采用

ADC12D1600 实现 6.4GSPS 采样的方案如图 2-2 所示,模拟信号经前端电路一分

为二送入两片 ADC 的输入端,ADC 工作在双沿采样模式,则两块 ADC 的采样时

钟均为 1.6GHz,且两块 ADC 的时钟相位差为 90°,然后将采样数据经 LVDS 并

行接口传输至后端按照采样时钟顺序重组数据,完成 6.4GSPS、12bits 数据采样。

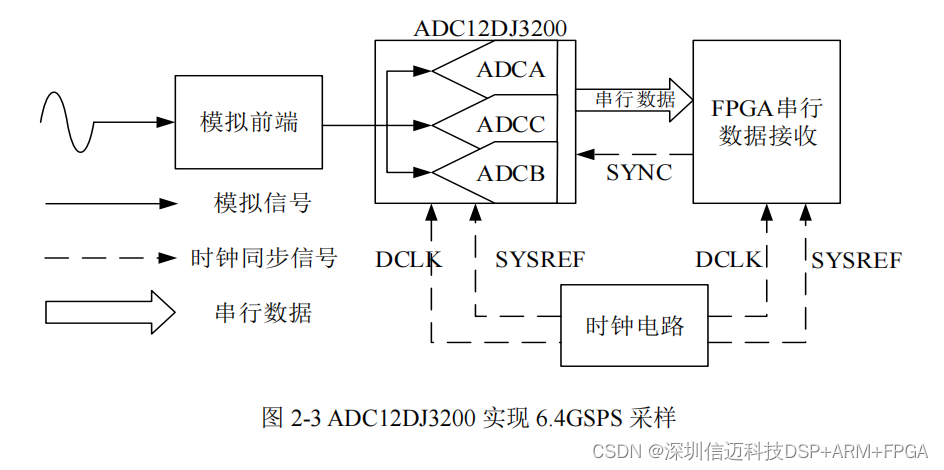

ADC12DJ3200 芯片内部集成了三个 ADC 内核,分别称为 ADC A、ADC B 及

ADC C,ADC C 通常用于后端误差校正模式时周期性地代替 ADC A 或者 ADC B

工作以保证正常采集[15]。因此,同 ADC12D1600 一样,ADC12DJ3200 也有两种工

作模式,当其工作在双沿采样(单通道)模式的时候便能实现最高 6.4GSPS 的采

样。ADC12DJ3200 采用 JESD204B 数据输出接口以应对数据速率的提升。

JESD204B 采用 CDR 技术(Clock Data Recovery,时钟数据恢复)从数据中恢复时

钟,因此没有时钟线,仅有数据线。ADC12DJ3200 最多有 16 条数据传输通道,

当工作在单通道模式时,可选择 8 通道或者 16 通道。由于没有同步时钟信号,

JESD204B 子类 1 通过系统参考时钟及同步信号实现同步功能。因此,对采用

JESD204B 子类 1 实现采样数据传输的采集模块,其时钟电路不仅需要提供 ADC

及 FPGA 的工作时钟用于完成数据采样,解串及恢复,而且需要提供系统参考时

钟用于产生衍生时钟,与同步信号一起完成链路建立及同步。图 2-3 为采用

ADC12DJ3200 实现 6.4GSPS 采样的方案。

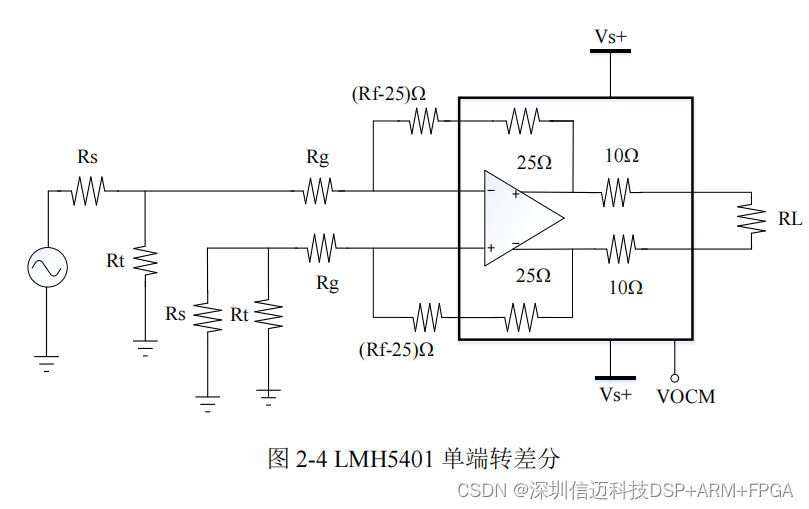

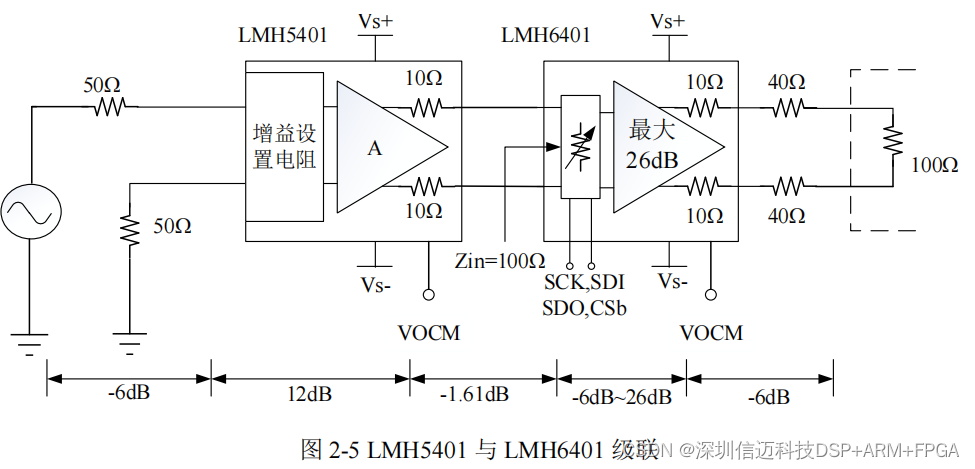

LMH5401是一款可使用外部电阻设置增益的全差分放大器[16],在增益为4V/V

(12dB)时,可实现6GHz的最大信号带宽。本文采用LMH5401实现直流耦合的单

端信号转差分信号,电路如图2-4所示,接地端经与输入源电阻同阻值的电阻接地,

以使输入阻抗与给定源阻抗匹配。

LMH5401输出和LMH6401输入之间的接口具有1.61dB的电压损耗,则在LMH6401

内部10 电阻之前输出的电压增益范围为-1.61dB至30.39dB。由于输入端损耗为

6dB,则输入端电压增益范围为-7.61dB至24.39dB,满足0dB至18dB增益要求。

由上述分析可得本文不同量程对应的 LMH6401 增益设置值,如表 2-1 所示。

2.3 高速采样时钟方案

2.3.1 JESD204B 时钟

数据采集模块的性能受 ADC 芯片性能影响,而 ADC 芯片性能又受时钟信号

质量影响,因此提高时钟信号质量至关重要。上文 ADC 芯片选型部分已在采集方

案实现上体现出两种数据接口的主要不同之处——时钟。采用 LVDS 并行传输方

式的采集系统,其高频采样时钟不仅会送入采集内部电路用于驱动 ADC 进行数据

采集,而且会经过 ADC 内部电路产生与采集数据同步的时钟信号一并送入 FPGA,

FPGA 内部的数据接收、处理采用的主时钟正是该同步时钟。不同于 LVDS 并行传

输方式的采集系统,采用 JESD204B 串行传输方式的采集系统要求既有送入 ADC

端的设备时钟还有送入 FPGA 端的设备时钟,这两个时钟频率可以不同但需要保

证同源。除了上述两种设备时钟,JESD204B 标准还需要用于同步的时钟等信号。

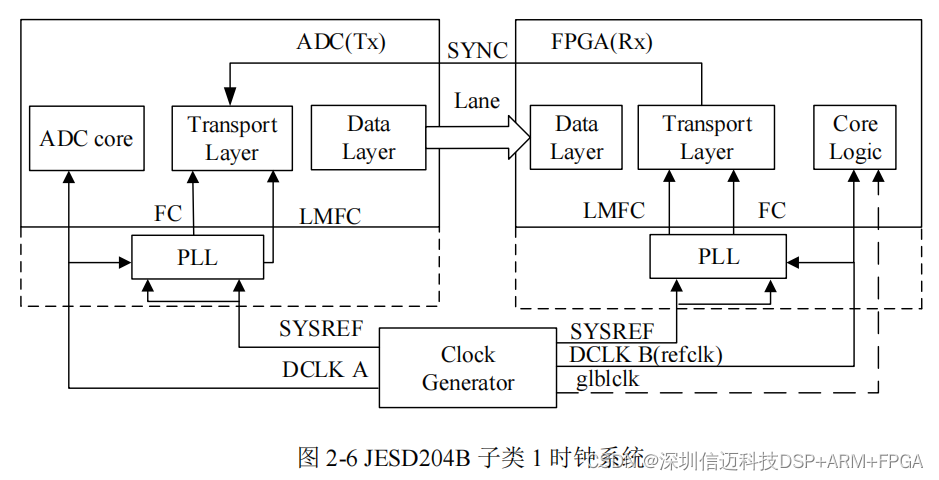

JESD204B 子类 1 要求 ADC 及 FPGA 两端都要有系统参考 SYSREF,以及一个

SYNC 信号用于 ADC 端与 FPGA 端的链路同步。一般 JESD204B 子类 1 的时钟仅

需设备时钟及系统参考,但是受 FPGA 型号及 JESD204B 链路的速度影响,FPGA

端有时还需要使用全局时钟。

ADC12DJ3200 的数据传输接口采用的是 JESD204B 子类 1,图 2-6 给出了典

型的 JESD204B 子类 1 时钟系统,其中包括设备时钟(DCLK),系统参考(

SYSREF)

帧时钟 FC(Frame Clock,FC),本地多帧时钟 LMFC(Local Multi-Frame Clock,

LMFC)以及全局时钟 glbclk。

送入 ADC 端的设备时钟(DCLK A)又称为采样时钟,用于 ADC 采样;送入

FPGA 端的设备时钟(DCLK B)又称为参考时钟(refclk),用作 JESD204B 协议

的物理层——GTP/GTX/GTH 串行高速收发器正常工作的参考时钟,该参考时钟频

率由串行线速率(Serial Line Rate)确定,同一串行线速率下有多个值可供选择。

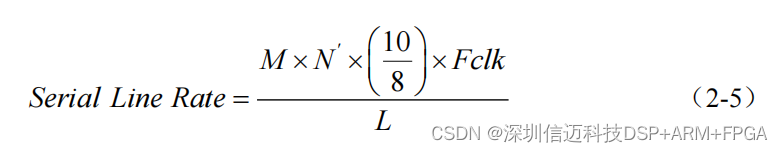

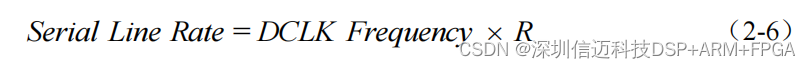

串行线速率指的是 JESD204B 各通道的数据传输速率,公式(

2-5)是计算该值的 通用方法。

其中,M 表示链路上转换器的数量,N’表示单个样本内信息位的数量,包括样本

分辨率、控制位和结束位,Fclk 表示器件或采样时钟,L 表示通道数,10/8 表示

8b/10b 编码的链路开销。对于本文采用的 ADC12DJ3200 器件,其串行线速率既可

以采用上式,也可以采用公式(2-6),因为 ADC12DJ3200 根据其操作模式定义

了 18 种 JESD204B 链路工作模式,简称为 JMODE,并罗列了相关参数。式(2-6)

中的 DCLK Frequency 为 ADC 采样时钟,R 为每个采样周期每个通道传输的比特

数。本文的采样率为 6.4GSPS,ADC 采用 JMOD1 模式时,采样时钟为采样率的

一半,即 3.2GHz,R 为 2,则串行线速率为 6.4Gbps。

2.3.2 时钟参数计算

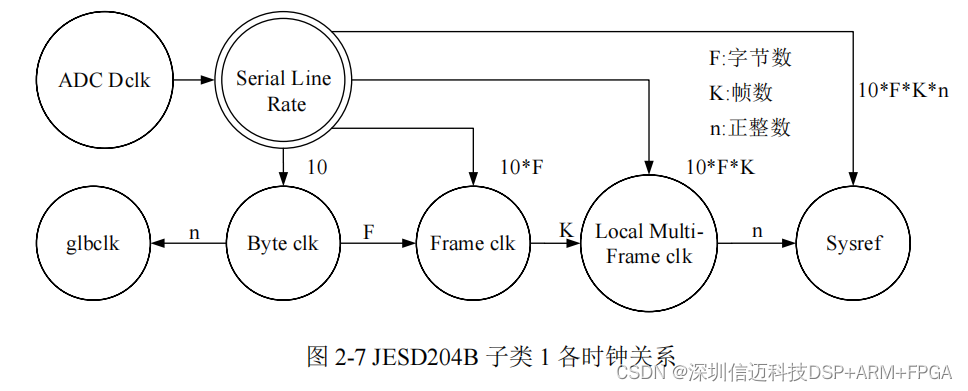

从 JESD204B 时钟系统可见帧时钟、多帧时钟等为设备时钟的衍生时钟,帧

时钟、多帧时钟等与设备时钟之间存在着一定的数值关系,图 2-7 描述了这些时钟

之间的关系。

由图 2-7 可知,在 JESD204B 时钟系统中,串行线速率是一个重要的参数,各

个时钟的频率都与该参数有关。下面介绍各时钟的作用及计算方法,首先是 ADC

及 FPGA 两端都有的时钟信号,再是 FPGA 端特有的时钟信号。

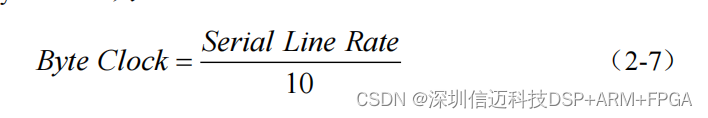

字节时钟(Byte Clock)是数据传输通道的字节速率。为了直流均衡,

JESD204B

的数据链路层设置了 8b/10b 编解码,数据传输通道的串行数据是 8 位传输数据经

过编码后的 10 位数据,由此可以通过串行线速率计算字节时钟频率,计算公式如

(2-7)所示。本文的 Byte Clock 为 640MHz。

帧时钟是 JESD204B 数据帧的传输速率。JESD204B 将传输数据按照每帧多少

个字节进行打包,帧时钟大小既可以通过字节时钟计算也可以通过串行线速率计

算得到,计算帧时钟大小的公式如(2-8)所示,其中 F 代表多少个字节为一帧数

据。本文的 F 为 8,则 Frame Clock 为 80MHz。帧时钟是设备时钟的分频。

2.4.2 数据存储结构方案

本文采集模块包含两个通道,各通道采样率为6.4GSPS,分辨率为12bits。将

数据位宽扩展至16位,则该模块的波形数据速率为6.4GHz 16bits 2,即25.6GB/s。

因为FPGA中单个DDR存储器控制接口最多支持64位数据位宽,则由波形数据速率

可以计算出使用64位DDR实现相同吞吐量时DDR数据速率高达3200MT/s。随着计

算机技术进步,DDR SDRAM的数据速率有了大幅提升,早期的DDR2最大数据速

率为800MT/s,DDR3的最大数据速率则为2133MT/s,DDR4的数据速率可以达到

3200MT/s。上述计算的DDR数据速率恰为DDR4可达到的最高数据速率。由于DDR

需要定期“刷新”,阻碍正常访存,降低工作效率,在计算DDR数据速率时需留

有裕量,故采用数据速率为3200MT/s的DDR4并不能满足需求。当数据速率已超过

DDR能提供的最高速率时,可通过扩宽DDR存储器的数据位宽达到提高数据吞吐

量的目的。将数据位宽从64位拓展至128位,由采集数据吞吐量可计算出此时DDR

数据速率已从3200MT/s降至1600MT/s,即(25.6GB/s)/128bits。实现时,使用两

个位宽为64位的DDR进行存储,两通道分别对应一个DDR。由单通道采集数据吞

吐量计算每个DDR的数据速率,单个 DDR的数据速率仍为1600MT/s,即

(6.4GHz 16bits)/64bits,可采用DDR3实现数据缓存。同样,考虑DDR的“刷新”

时间,以91.03%的访问效率计算[21],则DDR3的数据速率应为1757MT/s。最终,

选择数据速率为1866MT/s的DDR3作为外部存储设备。

使用DDR3实现的具体方案有如下两种:一种是采用8片位宽为16位,数据率

为1866MT/s的DDR3颗粒,每4片颗粒并联为一组用于一条通道的数据存储;另一

种是采用两片位宽64位、数据率1866MT/s的DDR3内存条,一片内存条对应一条通

道的数据存储。存储容量上,DDR3颗粒单片最大容量可达4000Mb,单通道4片并

联存储容量便能达到2GB;DDR3内存条最大容量可达8GB。因此这两种方案都能

满足数据速率及容量要求。采用DDR颗粒方式与采用DDR内存条的方式区别主要

在电路设计上,DDR颗粒通过直接焊接颗粒在电路板上实现,而DDR内存条采用

插槽实现,插槽方式便于器件更换。最终,选择镁光公司的DDR3内存条——

MT8KTF51264HZ-1G9,其内存容量为4GByte,数据速率为1866MT/s,数据位宽

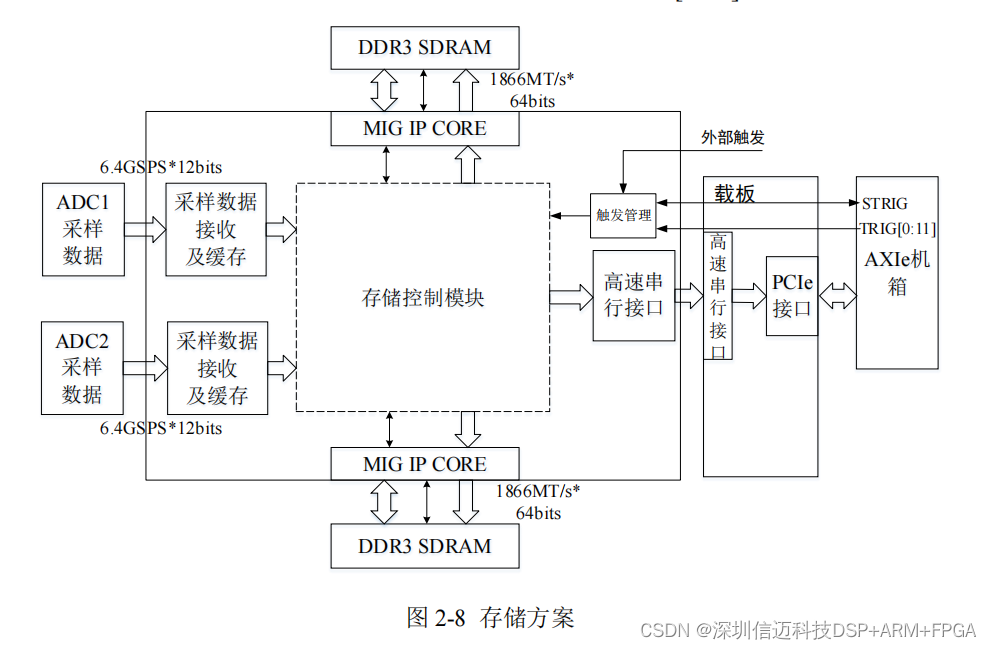

为64bits。存储方案如图2-8所示,两路ADC采集数据经JESD204B链路传输至FPGA

内部,再经异步FIFO跨时钟域和缓存处理后进入存储控制模块,存储控制模块根

据操作命令及起始地址实现连续多段存储、读取。存储控制模块将接收外部触发

信号和AXIe机箱提供的双向星型STRIG触发信号及TRIG[0:11]触发信号。