基于STM32 ARM+FPGA的电能质量分析仪方案(二)软件设计

本部分主要介绍FPGA+ARM控制部分的软件设计。FPGA+ARM控制部分包括Verilog

HDL硬件描述语言和C语言的开发。FPGA 部分主要控制AD7606模数转换、数字三相锁相

环和FFT谐波计算模块、SDRAM控制器的设计、FSMC接口模块等。ARM部分主要完成嵌

入式实时操作系统 FreeRTOS的移植、FPGA和ARM之间数据的读取和写入、ARM和上位机

之间的串口通信、以及经浮点运算后得出电能质量的各项参数等。

4.1 FPGA 模块软件设计

4.1.1 FPGA设计优势

FPGA 采用的是自顶向下的设计方法,将复杂的系统划分为低层次的功能模块,再将低

层次的模块划分为下一层的模块,一直划分直到能够使用基本模块为止。这种方式极大地

提高了开发效率和便于管理,使用 FPGA 开发具有很多优点:

(

1)运行速度高。FPGA 通过外部输入晶振产生系统时钟,再利用内部的锁相环倍频

功能可以生成各模块所需的时钟,频率可以达到很高。

(

2)代码运行效率高。与单片机、DSP 不同,FPGA 打破了传统的顺序执行模式,采

用硬件并行执行方式,其运行效率更高。

(

3)数字接口丰富。FPGA 的 I/O 口众多,能够完成大规模的系统设计,而且开发人

员可以自定义这些 I/O,使得 FPGA 的灵活性很高,其功耗低,输入输出接口能与 TTL、

CMOS 等兼容。

(

4)可重构。FPGA 的内部逻辑可以根据需求而改变,可以极大地缩短集成电路的设

计周期,还能够降低成本,市场前景广阔。

4.1.2 FPGA开发语言及软件

Verilog HDL是一种硬件描述语言 [45],用来描述数字系统硬件的结构和行为。和一般的

高级设计语言不同,硬件描述语言并行执行,还能描述过程中的时序,可以对各种抽象层

次的数字系统进行建模,这些层次按级别有系统级、算法级、RTL级、门级、开关级,在模

块中对设计的描述方式分为数据流、行为和结构三种方式,Verilog HDL于 1995 年被正式

纳入 IEEE 标准。

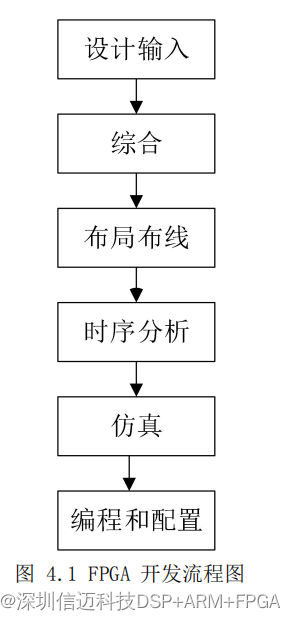

QuartusII是 Altera 公司的FPGA开发软件,输入形式包括原理图、Verilog HDL 等,其

界面友好且操作方便,涵盖了可编程逻辑器件的完整开发过程,包括设计输入、综合、布

局布线、时序分析、仿真和编程配置,用户可以在 QuartusII 中实现整个数字集成电路的

FPGA 设计流程。开发流程图如4.1所示。

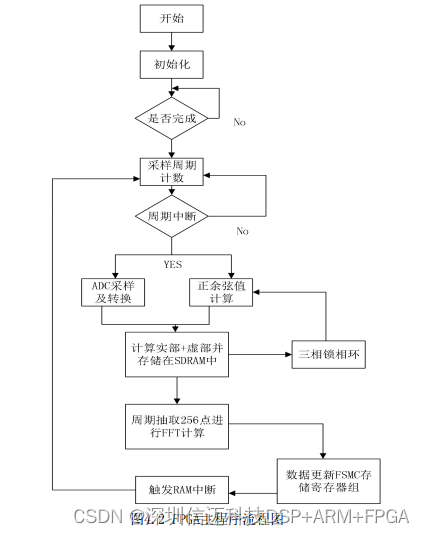

4.1.3 FPGA软件运行流程

(1)设备上电后,复位,完成初始化。PLL锁相环将输入的25MHz晶振时钟倍频到

100MHz,作为系统运行的主时钟。PLL输出稳定后,主状态机开始运行,并等待AD7606初

始化完成后,设备正式开始运行。

(

2)采样周期计数模块产生一个周期中断作为AD7606的采样频率,中断频率大小由三

相锁相环的输出决定(初始值为100MHz/12.8KHz=7812)。

(

3)ADC采集模块接收到周期中断后,立刻开始同步采集并转换3路电压和3路电流信

号 ,转换方程如下:( 5 ) =

32768

5

5

V

I

N R

E

F

V CODE

V

V

。同时正余弦计算模块,根据三相锁

相环输出的锁定相位角(初始值为0),计算1-17次谐波的正余弦值。

(

4)SDRAM计算模块,将AD采样的三相电流和正余弦值作为输入,计算出其实部和

虚部,然后将其存储在SDRAM中。

(5)FFT计算模块,以一定的周期,在SDRAM模块中,抽取三相电流数据点,分别进

行256点FFT计算,然后将计算出的三相电流谐波分量幅值,存入到RAM中。

(6)三相锁相环模块,对AD采样的三相电压,进行锁相环计算,并输出采样频率,通

过该值调整AD的采样频率,使当前正余弦值计算模块的相角与三相电压同相。

(7)最后将所有的计算数据同步更新到FSMC的存储寄存器组中,并输出一个ARM中

断信号,通知ARM对这些寄存器数据进行访问。步骤3-7,必须在下一个周期中断产生之前

完成。步骤3-6完成后,主状态机将等待下一个周期中断,然后重复以上步骤继续运行。

FPGA主程序流程图如4.2所示。

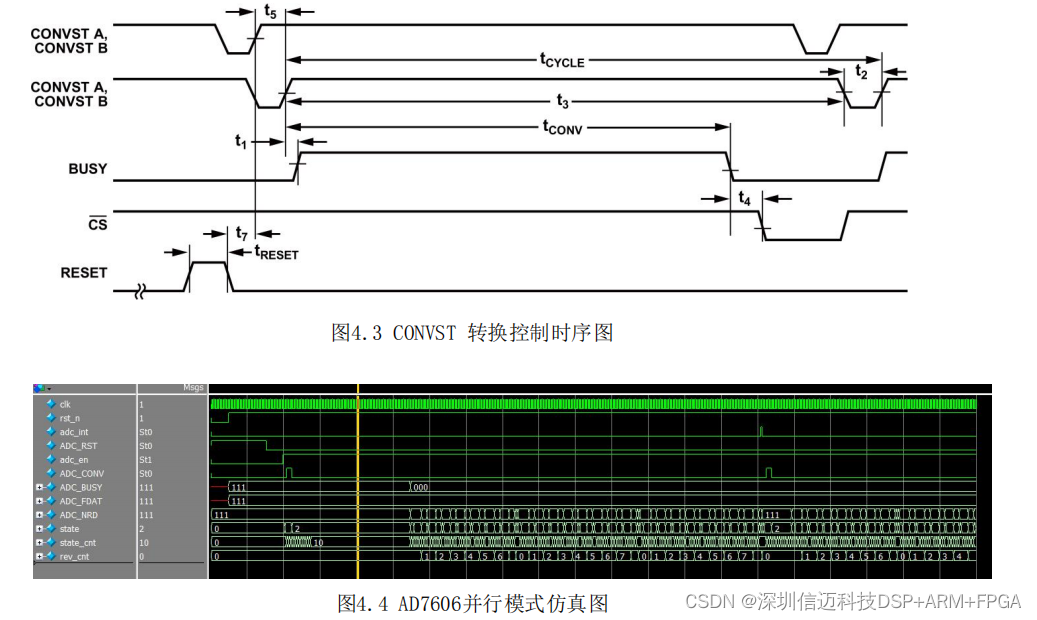

4.1.4 AD7606 采样

AD7606 的工作是通过 FPGA 控制其信号时序进行的。AD7606通过CONVST_A、

CONVST_B 引脚分别控制V1~V4、V5~V8八个通道的转换,通过 CS 和 RD 控制数据的读

取,通过PAR/SER SEL引脚控制选择数据接口模式。本设计中将 CONVST_A、CONVST_B

连接在一起实现 8 通道同步采样,将PAR/SER SEL引脚设置为低电平时采用并行数据线

DB[15: 0]输出。在开始采样之前,需要给RESET引脚一个大于50ns的正脉冲进行复位,当

CONVST信号的上升沿时AD转换开启,AD7606内含有的片内振荡器用来实现转换,同时

BUSY信号变为高电平并发送至FPGA表示正在进行数据转换,当转换结束时BUSY信号恢复

低电平,此时8路转换数据被锁村到输出数据寄存器中,设置CS和RD设置为低电平,使能

数据输出总线DB[15:0]并将数据发送至FPGA,一次A/D 转换结束。BUSY 信号高电平的持

续时间_t__CONV_ 的长短取决于芯片的采样速率 ,转换控制时序如图 4.3所示。

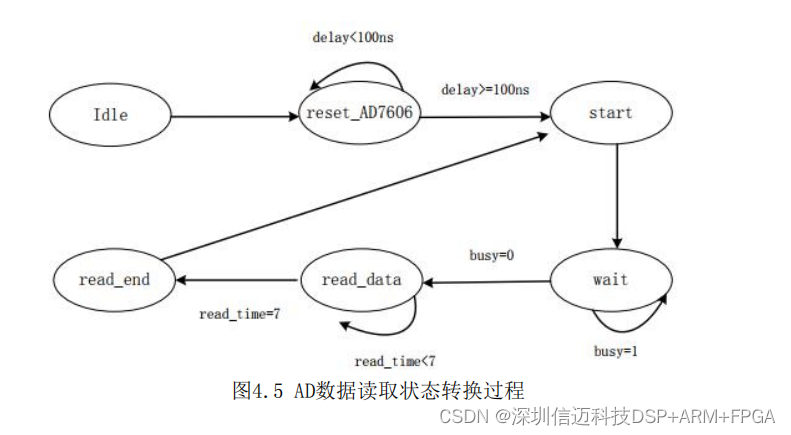

驱动程序的编写是利用FSM(

Finite State Machine,有限状态机)设计实现的,AD数

据读取状态转换过程如图 4.5 所示,关键程序部分见附录。

4.1.6 FFT运算模块

本设计中谐波计算采用基-2 FFT 变换,FFT运算模块有两种实现方法:第一种是根据

FFT的基本原理自定义FFT模块,设计模块有蝶形运算单元、旋转因子单元、地址发生器以

及时序控制单元等,然后再进行仿真测试,这种方式占用较多的资源,而且计算效率较

低;第二种是利用Quartus ii软件上提供了专门的 FFT IP 核,根据设计要求设置参数就能得

到一个高效地 FFT 模块,在实际工程应用中可以直接移植,在移植之前需要对其进行时序

仿真验证。本文选择第二种方法。

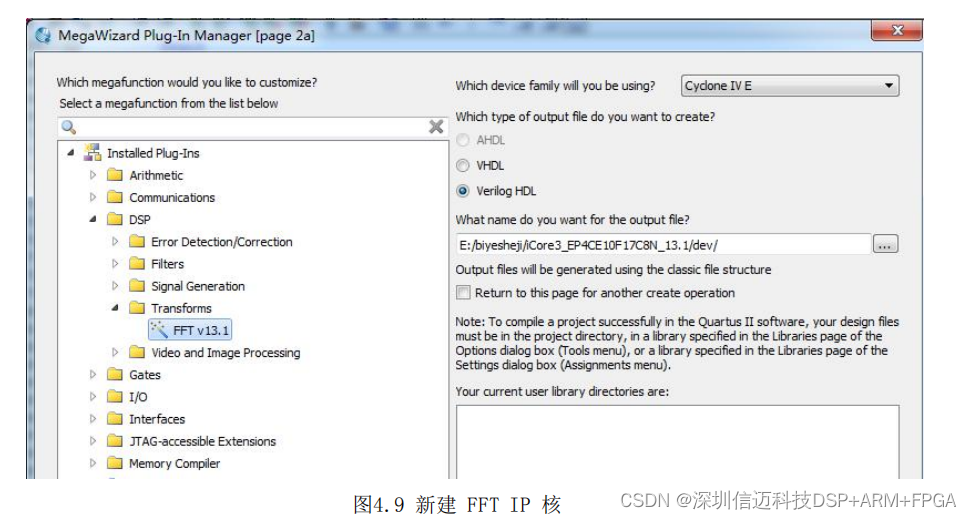

Quartus ii提供了两种定制FFT的方法:DSP Builder 和MegaWizard Plug-in Wizard,本

设计选择了第二种方法,其可以手动配置 FFT 的参数。选择 Transforms 下 FFT v13.1,选

择输出文件类型为 Verilog HDL [47],新建 FFT 如图 4.9 所示。

进入 FFT 配置界面后,配置的是转换长度为256点,数据位度和旋转因子精度都为

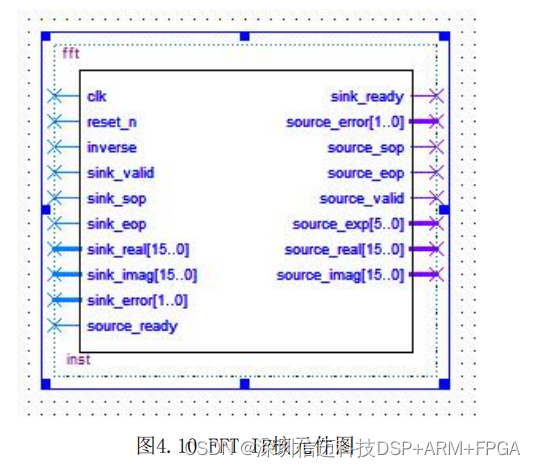

16bits。FFT IP核元件图如4.10所示,包含10个输入和8个输出信号:

sink_real[1 5:0]和sink_imag[1 5:0]:是输入数据的实部和虚部;

source_real[1 5:0]和source_imag[1 5:0]:是输出数据的实部和虚部;

Source_exp[5:0]:是所得输出实部和虚部数据的指数;

Sink_valid:为1时,表示FFT正接收数据;

Source_valid:为1时,表示正读取FFT的转换结果。

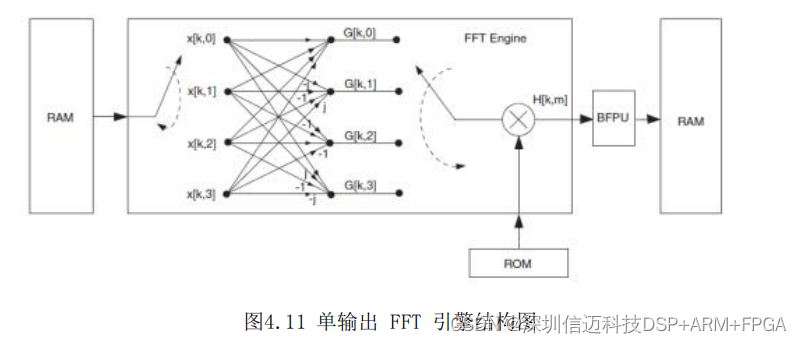

FFT核的引擎架构分为四输出和单输出,这里的“单”和“四”是指内部FFT蝶形处理

器的吞吐量,前者分时复用一个复数乘法器,单个时钟内得到1个输出,单输出消耗资源

少;后者同时使用4个复数乘法器,单个时钟内得到4个输出,四输出计算速度快。本设计

采用单输出引擎架构,可以使 FFT 处理器的资源消耗最小化。其中单输出实现结果如图

4.11 所示,FFT 引擎通过并行方式从 RAM 中读取复数输入x[k,i],然后通过蝶形运算得到

FFT 输出一路结果G[k,i]。

FFT 核内部数据使用块浮点结构,以达到高信噪比(SNR),Altera FFT 核可以设置

为四种 I/O 数据流结构,按不同的速度要求由高速到低速分别为流结构、变流结构、缓

冲突发结构、突发结构四种I/O 流方式。流结构和变流结构都是流水线型的,是对时间

要求很严格的应用场合,能实现很高的数据吞吐率,但缺点是占用最多的逻辑资源。硬

件实现的 FFT 处理速度快,即便是突发结构,1ms 内便可完成一次 256 点FFT,故选

择 Burst 架构。

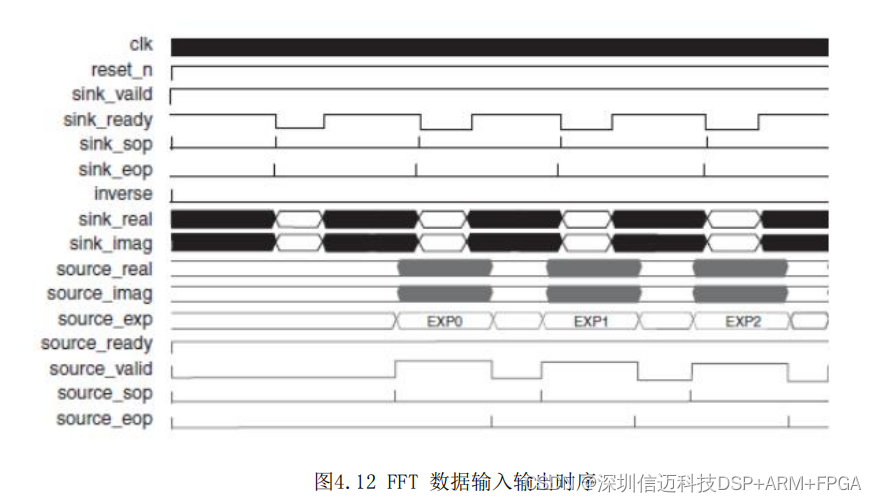

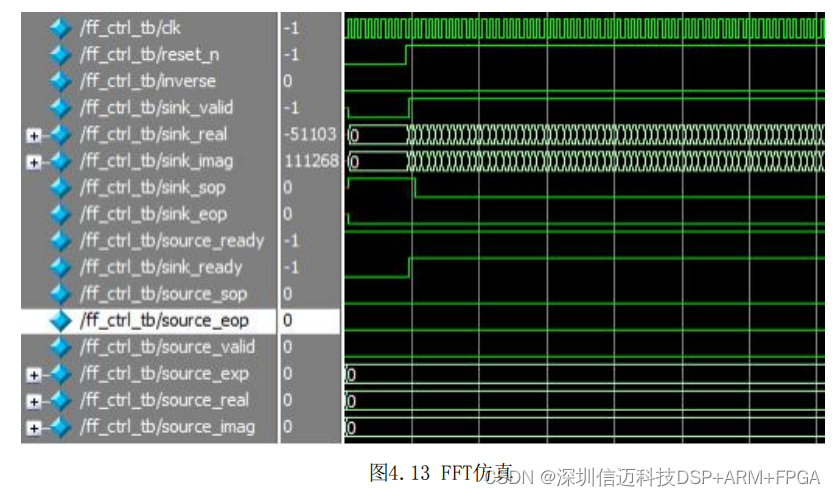

最后要对FFT仿真激励文件进行编写,利用Modelsim仿真软件,与Quartus ii 自带的

仿真功能不一样,Modelsim仿真需要编写激励文件(Testbench)。激励文件主要用于给子

模块提供信号激励。FFT数据输入输出时序如图 4.12 所示,仿真图如4.13所示,左侧为

模块端口变量名。

4.2 ARM 模块软件设计

4.2.1FreeRTOS简介

近年来嵌入式操作系统因其高实时性、多任务调度等优点在各个领域得到了广泛的应

用,目前主流的嵌入式操作系统有Vxworks、Linux、µC/OS-II及FreeRTOS等,不同于Unix

操作系统给每个任务分配同样的运行时间的任务调度方式,RTOS的任务调度设计是可预测

的,FreeRTOS的任务调度就是根据优先级来决定下一刻该运行哪个任务,这样在实时环境

中操作系统就能够对某一事件做出实时的响应。本设计采用FreeRTOS嵌入式实时操作系

统,可以更合理、更有效地利用CPU的资源,简化应用软件的设计,缩短系统开发时间,更

好地保证系统的实时性和可靠性。FreeRTOS是一个可裁剪的小型实时操作系统,其特点包

括:

(

1)性价比高。FreeRTOS是完全开源的操作系统,其完整的源码在官网就可以方便的

下载到。

(

2)高可移植性。FreeRTOS源码大多用C语言编写,移植起来更加方便。

(

3)可裁剪性。用户可根据FreeRTOS提供的丰富的配置,选择自己需要的内核功能。

(

4)混合任务调度模式。FreeRTOS同时支持优先级抢占式、轮转式协同调度和时间片

调度三种方式,优先级高的任务优先处理,优先级相同时则按时间片轮流执行,这样使得

系统运行时的灵活性强。

(

5)FreeRTOS系统简单、小巧,一般内核仅占用4k-9k字节空间,大大节约了资源。

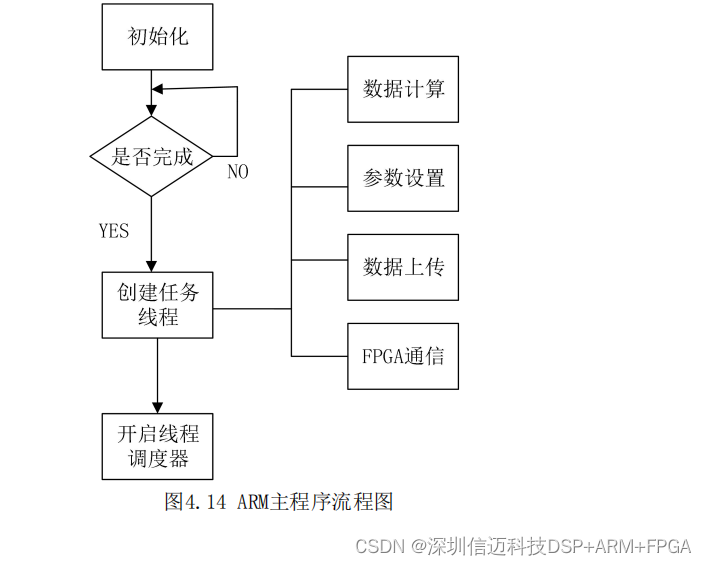

4.2.2 ARM软件运行流程

ARM上电后执行以下初始化:FreeRTOS内核初始化、板载信号灯初始化、串口初始

化、FSMC总线初始化、中断IO初始化。

初始化完成后,将会创建4个线程:

(1)参数设置线程:ARM通过串口,接收上位机设置的参数,并执行响应操作。

(2)数据上传线程:ARM通过串口,将设备运行数据上传给上位机。

(3)FPGA通信线程:完成ARM向FPGA写入参数及ARM向FPGA读取数据。

(4)数据计算线程:计算FPGA上传的数据。

线程创建完成后,开启任务调度器,RTOS将调度上述三个线程进行运行,ARM主程序

流程图如4.14所示。

信迈提供STM32 ARM+FPGA的解决方案。

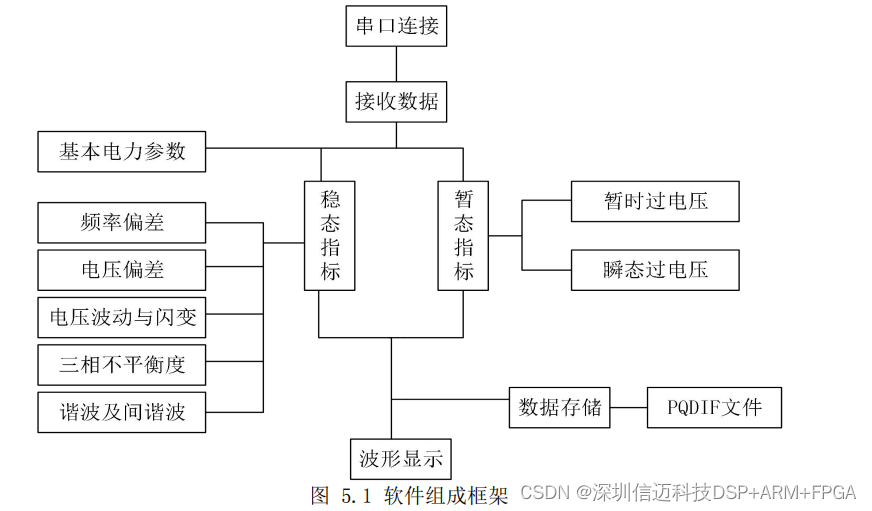

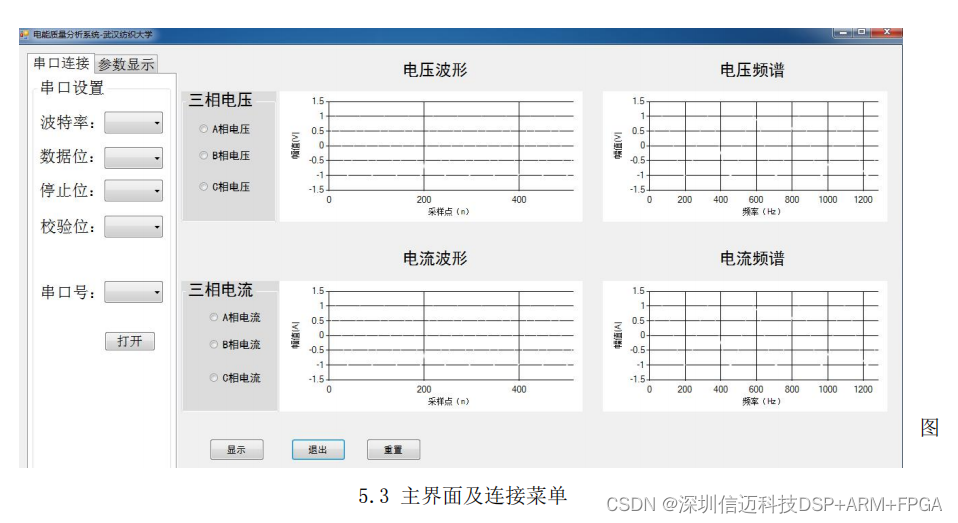

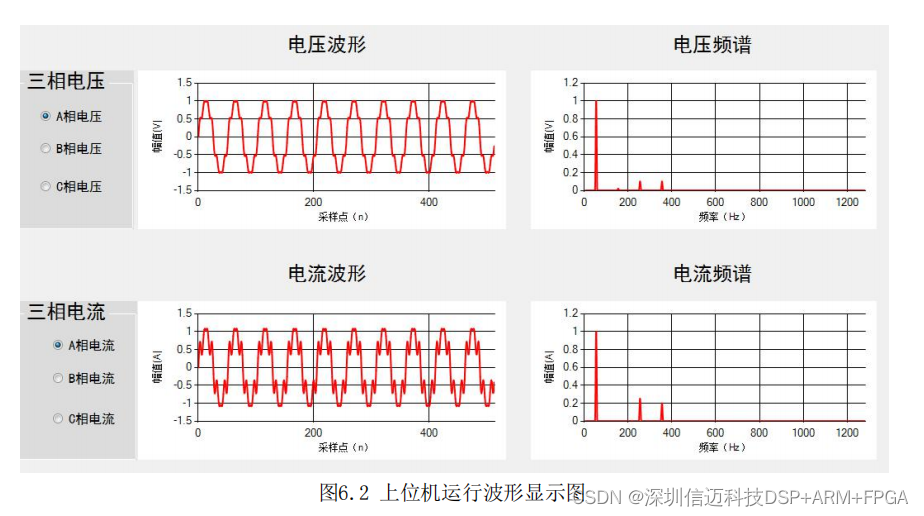

上位机软件主要实现功能是:接受串口发送的数据并发出指令,处理和存储通过串口

通信接收到的电能质量数据,并实现对电能质量指标和波形的显示和分析。

5.1 基本框架

本文上位机软件开发平台为 Microsoft Visual Studio 2013,开发语言为C#。C#语言具有

开发速度快、良好的面向对象的特性、基础类库全等优点 [48]。数据分析软件编写采用了模块

化设计思想,方便系统后期的功能更新,主要包括绘图部分、数据存储部分以及数据分析

部分。软件基本框架如图 5.1 所示。