STM32+FPGA的导常振动信号采集存储系统

摘要:针对工厂重要设备运输途中可能损坏的情况,本文设计了一套采用 STM32F103+FPGA 框架的无线传输的振动 信号采集存储系统,可以用于重要设备运输过程中异常振动的实时监测。首先将系统刚性连接在被运输设备上,通过三 轴振动传感器获得振动数据,FPGA 对数据进行采集、存储,STM32通过无线模块将数据发送至相应的上位机中、进行 相应的振动参数判断,以确定设备的运输状态。振动台实验与实际碰撞实验结果证明,该无线三轴振动信号采集存储系统能够应用于运输设备的异常振动监测,且具有易安装、测量快速准确等特点。

0 引 言

振动是一种普遍存在的现象。虽然利用振动特性生

产的振动筛[1]、压路机等设备给日常生活带来了许多便利,

但是更多的振动往往会破坏机械设备[2],比如在运输过程

中产生的异常振动往往会危害到运输设备的安全,为了确

保工厂某些重要设备运输的安全性,本文利用 STM32和

FPGA设计了一套无线三轴振动采集存储系统[3]。

目前,大多数振动监测设备都是通过有线的振动传感

器[4] 采集数据,但是运输过程中线缆不方便布置,数据不

能实时传输到上位机,对运输设备的异常振动情况不能做

到实时监测。

本文设计的无线三轴振动采集存储系统,以STM32F103

单片机为主要控制单元,采用三轴加速度传感器,FPGA 将

采集到的数据写入 FLASH,并且通过 SPI协议将数据发

送给STM32F103,STM32F103将采集到的数据通过无线

模块nRF24L01发送到上位机,上位机将数据进行分析显

示。本文以测试振动台[5] 为试验对象,将采集到的振动加

速度信号[6] 存入 FLASH,并且通过无线模块将数据发送

至上位机软件。系统预留了有线以太网口,确保数据能够

安全可靠地传输至上位机。

1 设计方案

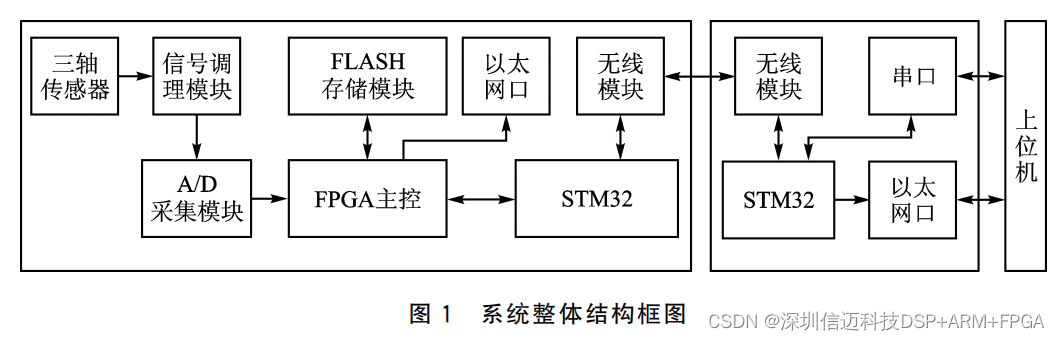

本系统主要分为采集存储模块和上 位 机 软 件 部 分。

系统整体结构框图如图1所示。

1.1 硬件设计

采集存储模块主要包括主控单元,以及信号采集、调

理、存储,数据发送,EEPROM 模块和供电模块。

① 主控单元。主控单元采用 STM32F103RCT6,FPGA

采 用 Spartan 6 系 列 的 XC6SLX16

CSG225,具有160个通用I/O。FPGA 与

STM32使 用 标 准 SPI协 议 进 行 通 信,

STM32F103RCT6通过无线模块接收上位

机软件的指令,然后通过SPI通知 FPGA

做出相应的操作。

② 信号采集。主要 是 三 轴 加 速 度

传感器与 A/D转换模块,采集到的信号

为振动加速度信号。加速度传感器的选

型主要考虑传感器的量程、灵敏度以及价格等因素,选择了

国产的 压 电 式IEPE 三 轴 加 速 度 传 感 器,其 产 品 型 号 为

A27F01Z。此款传感器的测量范围为±2000G,频率范围为

2~5000Hz,供电电压为5V,工作电流为2~10mA,正常

工作偏置电压为2.5V。

A/D转换模块采用的是 ADS8681,传感器信号经过

模拟板信号调理电路之后,进入 A/D 芯片转换成数字信

号之后存入 FLASH。三轴振动数据的采集采用3个16

位的 ADS8681,最大采样率为1 Msps,供电电压为3.3V

(数字供电)和5V(模拟供电),参考电压采用自身内 部

4.096V 的参考电压,其电路原理图如图2所示。

的主要器件为 AD8030运放。

④ 信 号 存 储。存 储 模 块 主 要

实现实 时 存 储 传 感 器 采 集 到 的 数

据,避免突然掉电等不可抗因素导

致的数据丢失。FLASH 采用 镁 光

公 司 的 非 易 失 性 NAND 型

MT29F4G08ABADA 闪 存 存 储 器

对 A/D转换的数据进行实时存储,

如图4所示。MT29F4G08ABADA的存储容量是4GB,内

部分成4096个块,每个块有64页,页编程时间为200μs,

数据写入速度约为8 Mbps,块擦除时间为2ms。

⑤ 数据发送。通过无 线 模 块 nRF24L01 发 送 数 据,

当前端 A/D采集到的数据大于设置阈值时,FPGA 将数

据 写 入 FLASH,并 通 过 SPI 将 数 据 传 输 给 STM32,

STM32将数据通过无线模块nRF24L01发送给上位机。

⑥ EEPROM 模块。EEPROM 主要是用于存储配置

参数(阈值、延 时 以 及 采 集 时 长),系 统 上 电 后,FPGA 从

EEPROM 中读取配置参数,将其设置成相对应的参数。

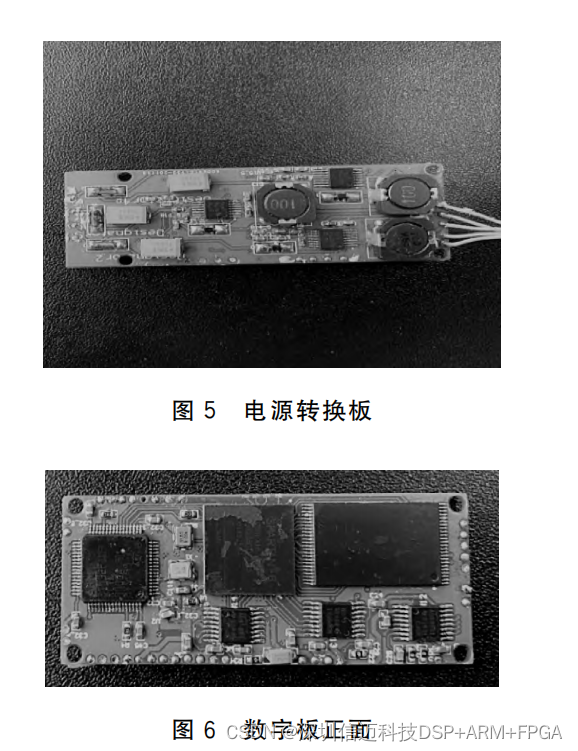

⑦ 电源模块。采用单独一块电源转换电路板给系统

供电,如图5所示。外部电源采用3.7V可充电

锂电池供电。

在完成以上电路设计之后,制作了集成化

印制电路板,如图6和图7所示。

1.2 硬件程序设计

程序设计核心部分是通过主控 FPGA 实时

监测 A/D数据输出,一旦 A/D输出数据大于预

先设置的阈值,FPGA 就将 A/D 输出数据写入

FLASH,采集时长为预先设定值。同时,FPGA

通过SPI协议将数据传输给 STM32,STM32通

过无线模块将数据传输至上位 机,系 统 程 序 流

程图如图8所示。

1.3 上位机软件设计

上位机软件主要通过无线接收终端对系统进行配置、

查询以及数据接收处理。

① 配置。上位机通过无线接收终端向下位机发送配

置指令,配置信息包括采集时长以及 A/D阈值。

② 查询。上位机通过无线接收终端向下位机发送查

询指令,下位机接收到之后通过串口返回配置信息(若未

配置,则返回值全1)。

③ 数据接收处理。上位机通过无线接收终端将接收

到的数据进行实时显示。

2 实际碰撞试验与振动台测试及结果分析

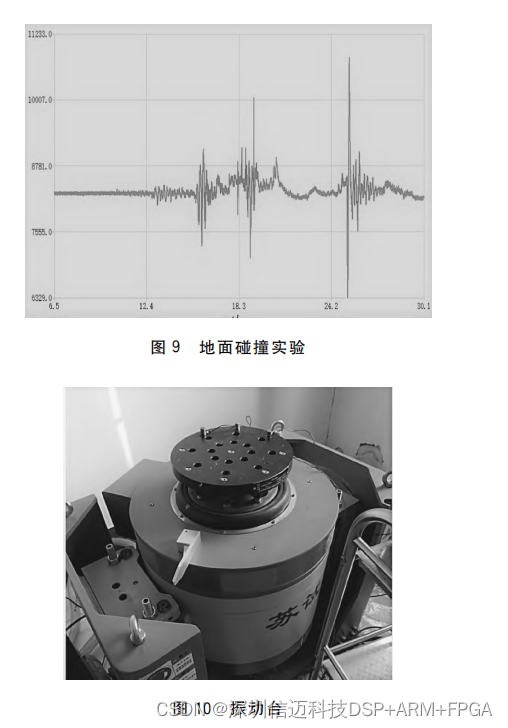

2.1 实际碰撞试验

为了模拟设备在实际运输过程中因为碰撞产生的振

动,将系统与地面以一定加速度使其发生碰撞,此时系统

设置的 A/D阈值为5g,上位机接收到系统因碰撞而产生

的振动信号如图9所示。

由图9可知,本系统对碰撞产生 的 振 动 信 号 比 较 灵

敏,能够较好地将信号采集并转发至上位机。图中,横坐

标为采样时长,纵坐标为 A/D量化值。

2.2 振动台测试结果

本系统使用振动台来验证系统的可用性,选择苏州苏

实试验仪器有限公司生产的型号为 TBR 300B、台体型

号为 DC 1000 15的振动台,如图10所示。

首先,利用上位机软件配置好阈值和采样时长,将系

统安装固定在振动台上之后,将振动台设置成不同大小加

速度环境下验证系统的可用性。

当振动台振动大于系统设置的 A/D 阈值时,系统通

过无线模块将数据上传至上位机软件,上位机软件将数据

显示出来,以达到实时监测的目的。

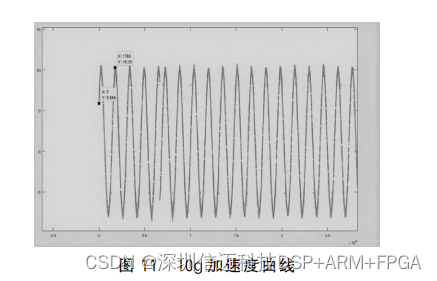

图11 10g加速度曲线

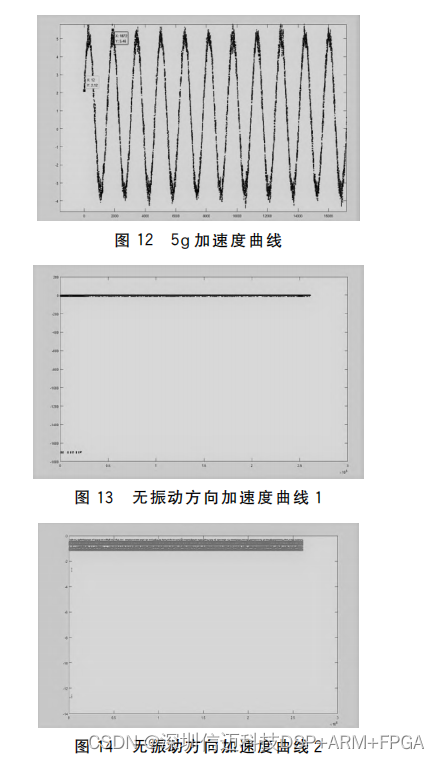

图11、图12所示分别是系统在阈值为6g、振动台加

速度为10g,以及阈值2g、振动台加速度为5g的振动数据

曲线。图13、图14分别是系统另外两个轴的振动曲线。

图15是系统在阈值为9g、振动台加速度为14.5g环境下

的振动数据曲线。图16是系统在阈值为3g、振动台加速

度为7.5g环境下的振动数据曲线。

4 结 语

本文通过研 究 LDPC 编 码 原 理,设 计 电 路 实 现 其 在

FPGA 硬件的板级验证,并在此基础上通过 EDA 工具完

成后端的自动布局布线流程。通过分析验证,完成工程的

芯片化制作,并通过板级验证得到完整的8176位的编码,

解决了 LDPC编码在硬件实现上的问题,提出一种新型编

码方案,利用IC设计实现从宏观到微观的操作流程,为探

索芯片国产化进程添砖加瓦。