ARM +FPGA GPIB IP核实现

目前在数据发生其技术上居领先的是美国的 Tektronix 公司和 Agilent

公司。

Agilent 公司的台式脉冲/数据发生器家族的最高时钟频率达 3GHz(定

时发生器),数据发生器 E81200 在通道数为 8CH 时数据速率为 660Mb/s,

即可以产生最高达 330MHz 的波形输出。

Tektronix 公司典型的台式数据发生器 Tek DG2020A,时钟频率为

200MHz,可以产生 100MHz 的图形数据输出,具有功能强大的波形编辑软

件。数据图形可由数据图形编辑器获得,编辑器包括了图形编辑器、定时

波形序列组合编辑器、表格编辑等波形编辑能力。国内一些高等院校和科

研单位正致力于研制数据发生器,有的可做到 100M 可编程数字信号,但

由于产品设计与生产工艺的不足,目前还未能形成数据发生器产品。

本文将围绕高速数据发生器的GPIB接口设计而展开,拟用专用芯片

NAT9914和FPGA两种方案实现GPIB通讯接口硬件部分,加上相应的接口软

件驱动程序,从而能容易的把该仪器与其它设备集成实现系统的自动测试。

2.1 高速数据发生器的主要工作原理

高速数据发生器由硬件和软件组成,以下是整机硬件与软件的总体方

案及主要工作原理。

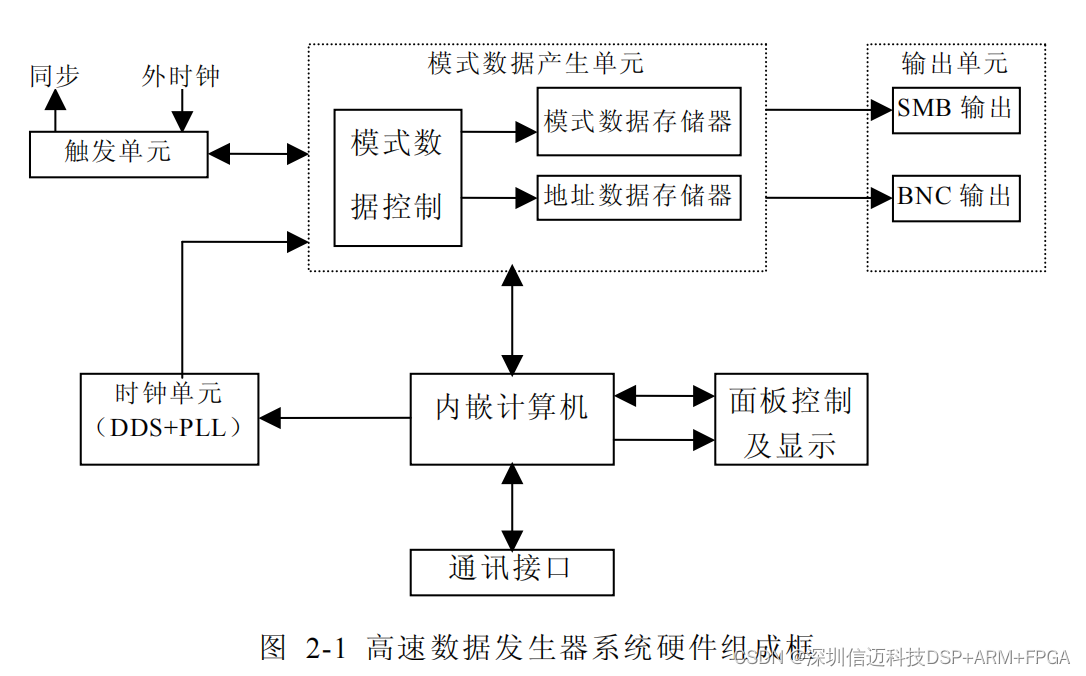

整个硬件系统以内嵌计算机为中心进行功能定义和模块划分,主要由

内嵌计算机、时钟单元、触发单元、模式数据产生单元、输出单元、面板

控制及显示、通信接口等组成。如图 2-1。

时钟单元采用 DDS+PLL 实现,它是整个高速数据发生器工作的基础,

其主要作用是产生频率连续可调的内时钟信号;模式数据产生单元包括模

式数据控制电路、模式数据存储器和地址数据存储器三个组成部分,其中,

模式数据控制电路是整个单元电路的核心,它控制数据的多路同时输出以

及序列数据的按序切换,采用专用 ASIC 电路设计,数据存储器采用高速

SRAM;触发单元用于输出同步时钟对外时钟进行变换;BNC 输出电路包

括模拟电路部分(即电平信息处理)、数字电路部分(即频率信息处理)、

末级驱动部分(信息合成输出)等三个组成部分;通信接口电路包括网口、

串口、GPIB 等接口,其中网口和串口是内嵌计算机自带,GPIB 接口采用

FPGA 或专用芯片实现。

3.2.5 设计芯片的选择

本设计采用 ALTERA 公司的 FPGA 芯片 ACEX1K30QC208 来实现。

1K30 芯片属 ALTERA 公司的 ACEX 系列,该系列是 ALTERA 公司着眼于

通信、音频处理及类似场合应用而推出的 FPGA 器件系列芯片,它采用

0 .22/0.18 微米混合工艺,密度从从 1 万门到 10 万门。它依然采用了

ALTERA 传统的 LUT(查找表)结合 EAB(嵌入式阵列块)结构,芯片包含一

个嵌入式阵列,可实现存储器和专用的逻辑功能,可实现单双端口 RAM

模式;一个 IOE 包含一个双向的 I/O 缓冲器和一个寄存器,IOE 可以配置

位为输入、输出、或双向管脚。

ACEX1K30QC208 的最大系统门数为 3 万门,它有 1728 个逻辑宏单

元数和 6 个嵌入式系统块,最大可提供 24567RAM 位,引脚数为 208 个,

除去一些配置引脚和电源引脚,实际可用的引脚数为 141 个,因而可完全

满足设计的要求。 [8]

一旦电路设计固定,将其电路设计写入配置存储片 EPROM 中,每次

上电后写入 FPGA 中,实现设计的电路功能。

3.3 系统的具体设计实现

3.3.1 总体框架

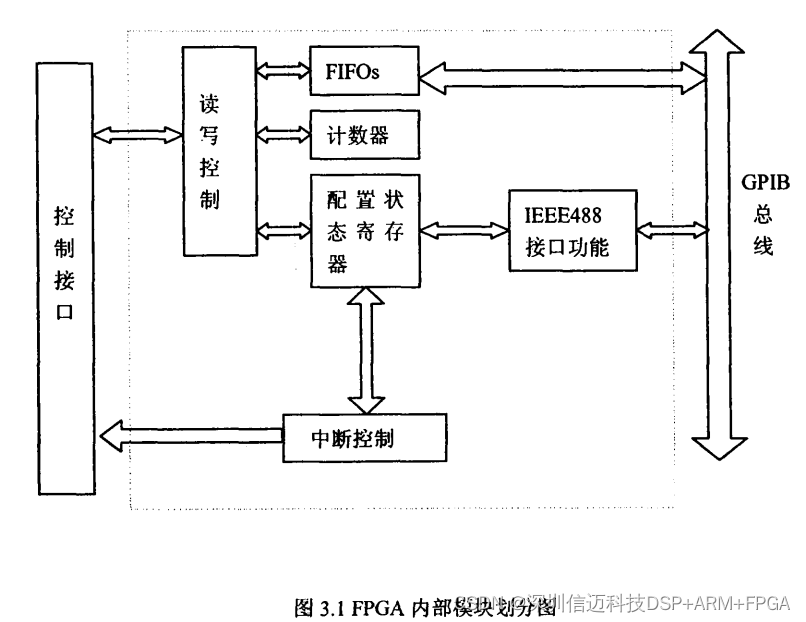

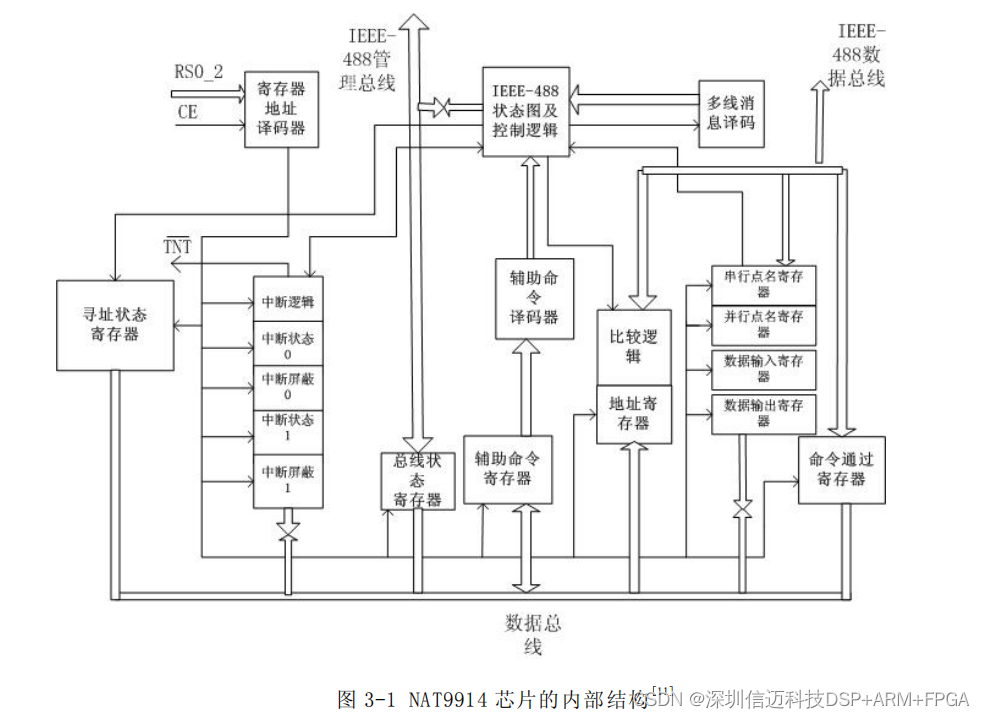

为了具有一定的通用性,高速数据发生器的 GPIB 接口设计主要参考

了 NAT9914 芯片的内部结构,内部结构如图 3-1 所示。我们把整个待设

计系统划分为若干基本功能模块单元进行设计,在基本单元实现方法上采

用语言描述方式完成,这不仅方便将来跨开发环境的移植,而且在功能调

试以及对局部修改都带来很大的方便。

我们可以把整个系统划分为几个子系统。其中包括和微处理器 ISA 接

口的控制逻辑,与 GPIB 母线通信的接口功能,数据通道部分。对每个子

系统的设计也可以采用向下分解为模块级设计,这样在调试和组件系统

时,不仅具有很强的灵活性,而且方便代码的调试以及利于代码的重利用。

ISA 接口的控制逻辑,将会在第四章详细的介绍,由于我们所选的

FPGA 芯片 ACEX1K30QC208 的逻辑宏单元数够大,所以可以将这部分下

载到 FPGA 芯片中,而不需要再用一片 EPM3128ATC100-10。这部分由于

后面阐述很详细,这里就不再赘述。

接口功能的设计是设计的核心,既是设计的重点又是难点。它不仅需

要对 IEEE488 协议有深刻的认识,而且,在接口功能子集的选择上也有一

定的要求。

数据通道部分有寄存器堆和组合功能电路,数据通道内部寄存器由 13

个寄存器组成,根据需要选择其中的 11 个,其中包括只读寄存器和只写

寄存器。它们是完成微处理器端到 GPIB 接口功能端的数据桥梁。该子系

统的设计亦是重点。

在完成基本模块以后,可以对每个模块生成图形化的符号(Symbol),

在组建整个系统的时候可以用类似画电路图的方法直接对这些符号进行

调用,设计相对直观而且对整个系统级架构的把握相对全面。在完成整个

内部电路的“软件”设计以后就是具体的把该“软件核”(CORE)固化到

具体选定的 FPGA 上,通常利用 JTAG 端口下载。

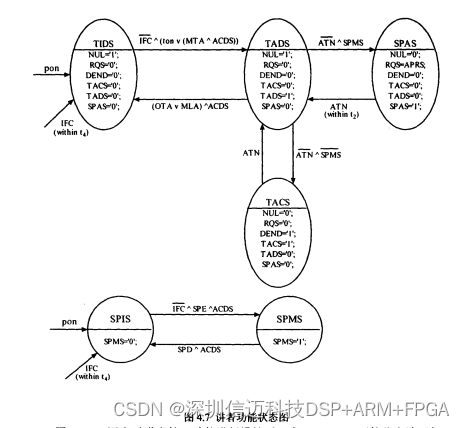

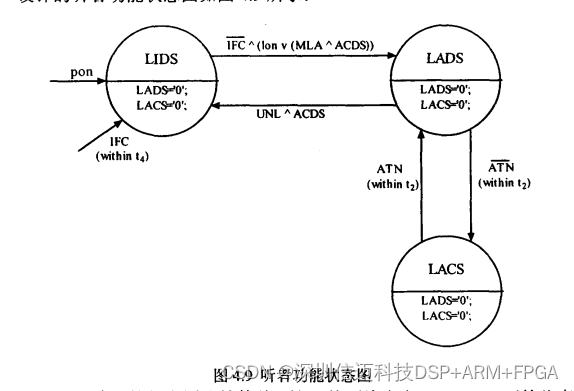

3.3.2 接口功能状态机实现

按照高速数据发生器要求,设计时选取了八种接口功能:源方挂钩 、

受方挂钩、讲者、听者、服务请求、远控本控、器件清除、器件触发。把

各接口功能划分为若干相关状态,这样在用 Verilog HDL 实现这些相互作

用影响的状态跃迁的时候就可以引入状态机设计。

一、状态机简介

[12]

状态机(FSM)从不同的角度有不同的分类方法。

从状态变迁的确定性来说,可分为确定型有限状态机和非确定型有限

状态机。从状态变迁的触发条件来说,可分为同步状态机和异步状态机,

同步状态机的触发条件限定为某预定时刻和信号(如系统时钟信号 clock),

输入信号的改变并不能立即产生相应的状态改变,异步状态机在任何时候

一旦输入信号改变的情况下都将发生状态变迁、产生相应输出。从状态机

的复杂程度来说,有单状态机(single FSM)和通信状态机之分,通信状态

机又可以分为主从通信状态机和并发通信状态机。单状态机从输入输出函

数关系来说,可以分为 Mealy 型和 Moore 型有限状态机,他们代表着最具

普遍意义上的有限状态机划分。

● Mealy 状态机和 Moore 状态机

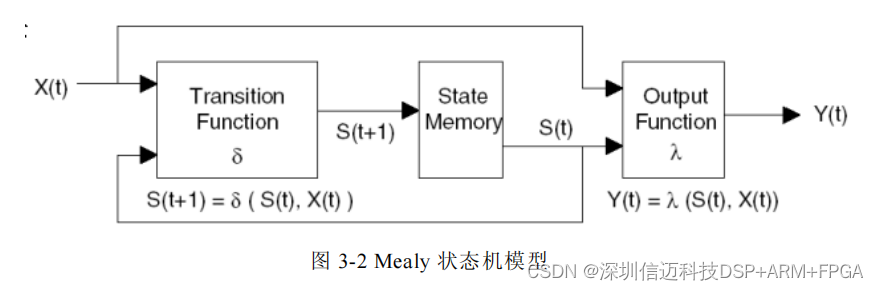

1、Mealy 状态机

Mealy 状态机的输出不仅仅是当前状态的函数,而且还是当前输入的

函数。图 3-2 是 Mealy 状态机的模型

2、Moore 状态机

Moore 状态机输出仅仅是当前状态的函数,与当前输入 X(t)无关,所

以 Moore 状态机是 Mealy 状态机的一种特例。图 3-3 是 moore 状态机的模

型。

一般来说 Mealy 型状态机的状态变量较少,状态变量少意味着采用较

少状态存储单元,在实际的工程应用中多数采用 Mealy 状态机。Moore 型

状态机易于代数分析,在 FSM 的代数理论中大都采用 Moore 型状态机作

为研究对象。

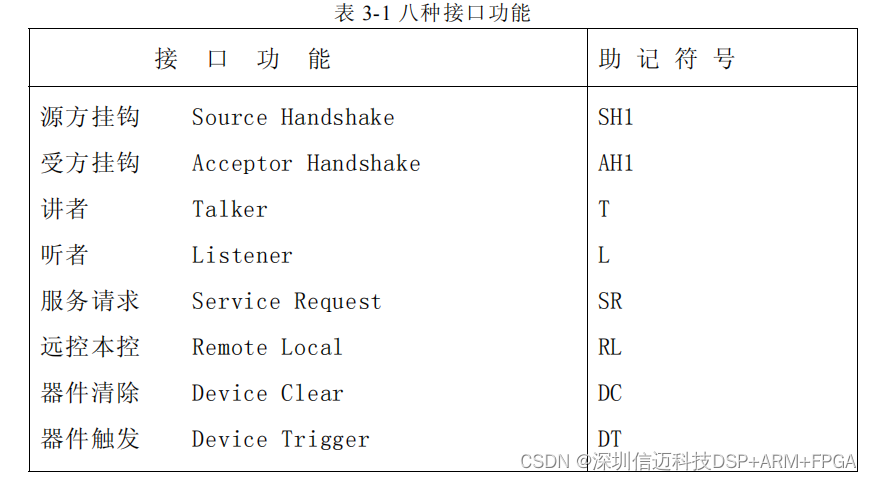

二、 接口功能的选取

在 IEEE488-1975 标准中规定了十种接口功能,每种接口功能按照特

殊的规约来行事。我们根据仪器的具体要求,选定八种接口功能,如表 3-1。