【AI服务器】全国产PCIe 5.0 Switch SerDes 测试和分析,以11槽PCIe GPU底板(PCIe 4.0/5.0)为例(一)

1 PCIe Gen 5 介绍

外围组件快速互连(通常称为 PCI Express 并缩

写为“PCIe”)是用于硬盘驱动、固态盘驱动(SSD)、

图形卡、Wi-Fi 和内部以太网连接的先进互联 I/O 技

术,包含一组快速、可扩展的、可靠的用于串行数据

传输总线的输入 / 输出标准。PCIe 的物理层也支持

快速串行高级技术附件(SATAe)和非易失性存储器

标准(Non-Volatile Memory Express,NVMe)。

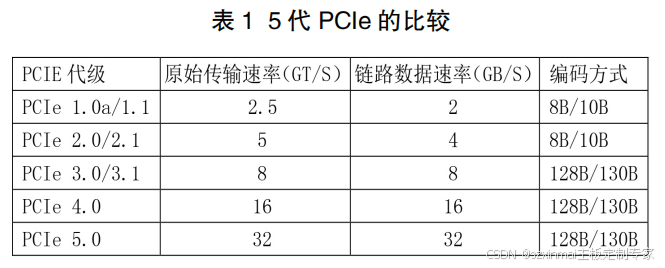

表 1 显示了 PCIe 数据速率的演进。从中看出,第

5 代 PCIe 5.0 比其上一代 PCIe 4.0 的吞吐量翻倍。

注:PCIe 2 的 8B/10B 编码方式变成 PCIe 3 的

128B/130B 编码方式,对应的开销从 20%变成小于

2%,原始传输速率从 5GT/s 变成 8GT/s,而链路数据

速率从 4GB/s 增到 8GB/s。

本文将介绍重要的 PCIe 5.0 SerDes 测试。其中,

关键测试设备由比特误码率测试仪(BERT)和示波

器组成。具体而言,PCIe5.0 测试需要一个仪表级的

脉冲码型发生器(PPG),可以精确注入特定的信号

损伤,以及一个误码检测器(ED),可以分析串行器 /

解串器(SerDes)输出比特误码率(BER),以确定其

是否符合 PCIe 规范。

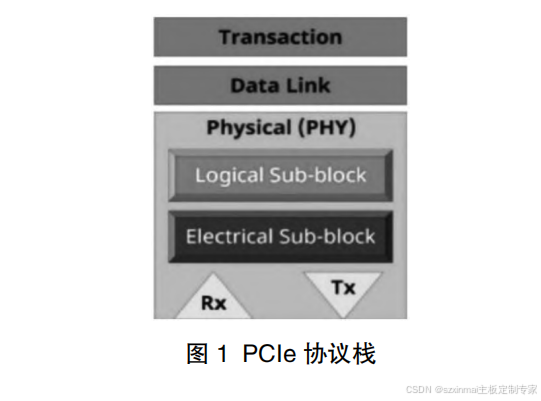

对于最复杂的 SerDes 测试,比如链路均衡训

练,BERT 必须能够模拟对应的 SerDes;PPG 和 ED

必须在 PCIe 5.0 协议栈的物理逻辑子块与被测设

备(DUT)交互(见图 1)。换句话说,BERT 必须具有

一定的协议感知功能。无论我们是在进行发射机测

试还是接收机测试,SerDes 的两个角色都涉及其

中;为了明确区分,我们将 DUT-SerDes 相应地称为

DUT- 发射机或 DUT- 接收机。

2 32 GT/s NRZ 的挑战

从 16 GT/s 的 PCIe 4.0 升级到 32 GT/s 的 PCIe

5.0 的最大挑战是,在规定的 BER<10-12 的情况下,

在高达 36 dB 的损耗时能正常工作。

为了缓解由损耗引起的问题,大多数运行速度

超过 30 GT/s 的标准都采用了 PAM4(4 电平脉冲幅

度调制),它的工作带宽降低到一半,但代价是信噪

比减少 9.5 dB 以上。而 PCIe 5.0 继续使用逻辑仿真、

不归零(NRZ)调制方案运行,该方案中逻辑 1 是高

电平和逻辑 0 是低电平。

在如此大的损耗下,PCIe 5.0 均衡后的眼睛张

开度可以低至 10mV;如此小的电压摆幅需要极为

灵敏的幅度判决器。为了适应电路板的长距离延伸,

当损耗超过 36dB 或信号通过两个或多个连接器传

输时,需要再定时器(Re-timer)。

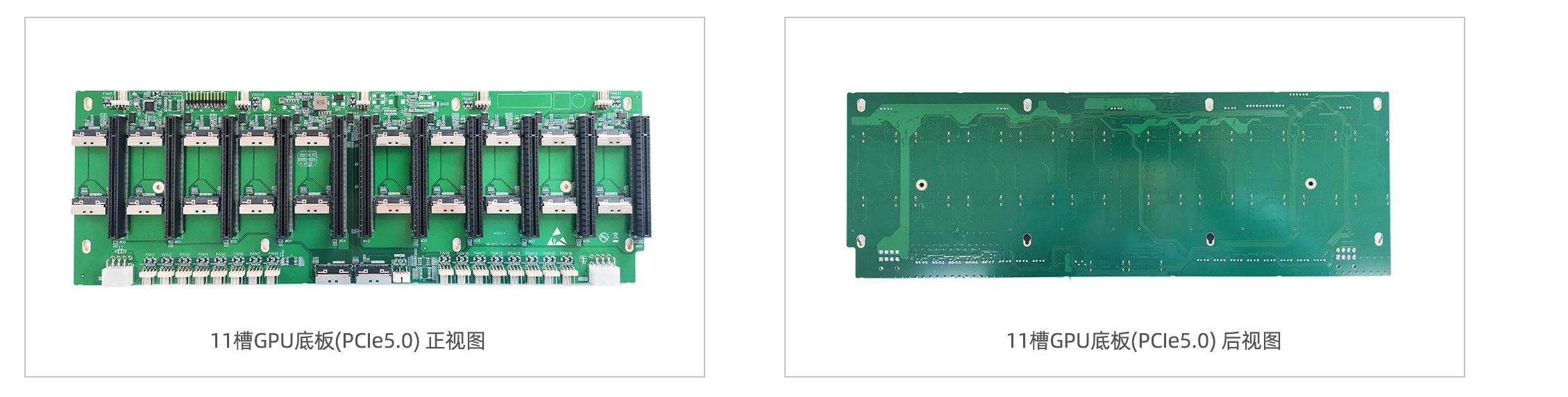

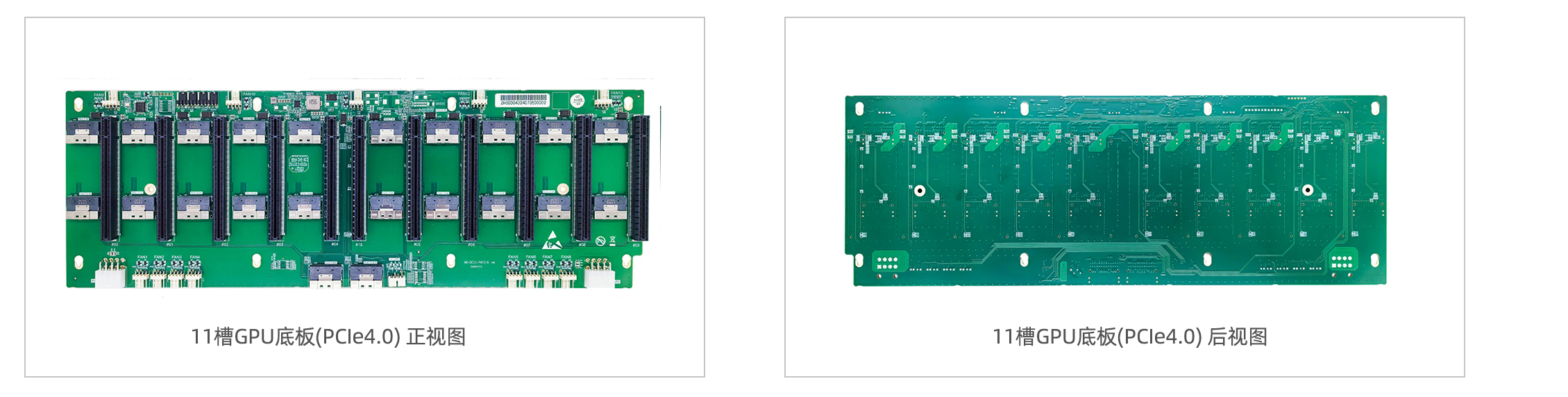

========================11槽PCIe GPU底板(PCIe 4.0/5.0)================

*10槽双宽和1槽单宽;

*11槽PCIe*5.0GPU底板;;

*每个槽采用MCIOx8*2或SFF8654x8*2

功能特性

产品规格

11槽 GPU底板(PCIe 5.0)

11槽 GPU底板(PCIe 4.0)

型号

MG-DC6-P5F216_V10

MG-DC6-P4F216_V10

输入接口

22*MCIOx8 PCIe5.0

22*SFF8654 PCIe4.0

PCIe插槽数

11* PCIe5.0 x16

电源接口

2* GPU 8PIN

IPMB接口

4Pin BMC I2C

尺寸

426(长) x 145(宽) x 2.5(高) (mm)

☑支持OEM/ODM定制服务