基于STM32+FPGA的地震数据采集器软件设计,支持RK3568+FPGA平台

0 引言

地震观测是地球物理观测的重点,是地震学和

地球物理学发展的基础[1]。地震数据采集器主要功

能是将地震计采集的地震波模拟信号转换为数字信

号并进行记录或传输[2],为地震学提供大量的基础

数据。本文将介绍基FPGA+ARM的地震数据采集器软

件设计。

1 研究背景

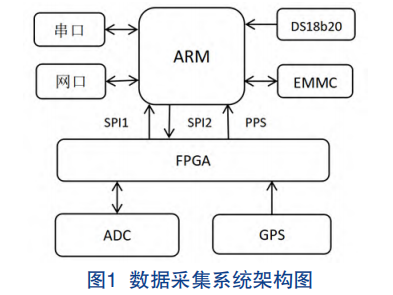

系统架构。本设计采用STM32MP157作为主控

制单元,运行在Linux环境中。ADC采集模块将地震

计产生的三分量地震模拟信号通过采样转换成数字

信号。FPGA 主要负责数据采集、数据传输和对ADC

参数控制,采集GPS模块接收的IRIG-B码,向ARM转

发PPS秒脉冲授时,FPGA和ARM之间SPI总线进行数

据交互,Linux驱动和应用层都运行在ARM上,主要

接收数据、数据处理、数据存储和数据传输,外接

EMMC用于储存数据,网口连接远程客户端。串口用

于帮助开发人员对开发板进行调试,DS18b20获取

环境温度。系统整体设计结构图如图1所示。

2 Linux平台构建

本设计采用虚拟机Linux系统方式开发,安

装Ubantu18.04操作系统,在vscode上编写驱动

和Linux应用程序代码,构建交叉编译器,移植

U-boot,裁剪官方Linux内核,使用Buildroot构

建根文件系统。STM32MP157移植5.4.31版本Linux

操作系统。开发测试过程中,板子使用串口连接

PC端MobaXterm调试,设置U-boot参数让设备树、

内核镜像均通过TFTP方式加载,从PC端虚拟机中

Ubantu的NFS共享目录加载根文件系统,测试时驱

动均以.ko模块的形式加载到内核。完成所有测试

之后,将驱动Linux内核,设备树、内核镜像、根

文件系统烧写进核心板内部EMMC中。

3 系统软件设计

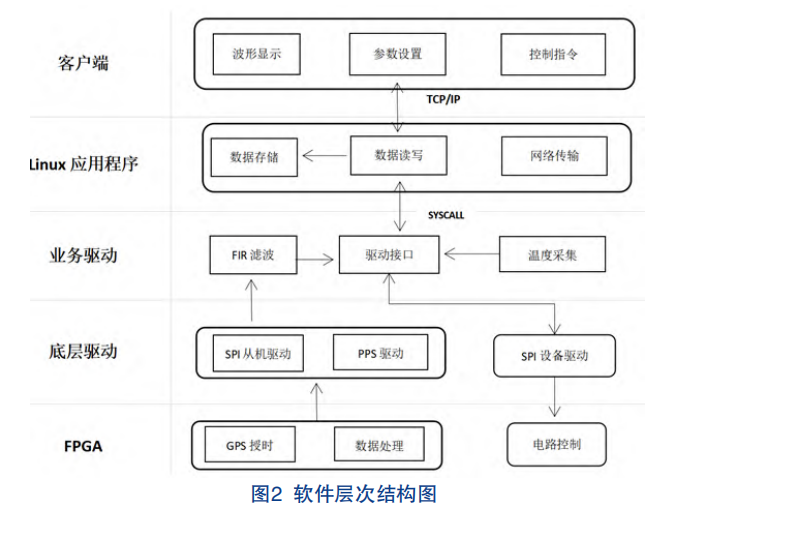

软件包括FPGA软件、ARM软件和客户端软件。

ARM软件包括驱动层和应用层,驱动有两层。(1)

与寄存器交互的底层驱动。(2)业务驱动层,主要

进行数据处理,编写系统调用接口,并在驱动中申

请为Linux系统/dev目录下的一个设备文件,Linux

应用程序通过系统调用联系驱动层,数据存储EMMC

中。通过网络与客户端建立连接,接收客户端数据

请求。客户端上位机软件主要用于显示波形、设置

参数和下达控制指令。软件结构如图2。

3.1 FPGA软件

FPGA芯片选用Intel Altera公司Cyclone系列

的EP4CE10F17C8N,在ISE软件使用Verilog语言编

程。FPGA采集AD芯片ADS1281的地震波数字信号,

ADS1281完成一次模数转换后,DADY引脚电平拉

低,FPGA可读取数据,实际采集有效位数为24 位。

GPS模块上电后会接收IRIG-B时间串码,一帧100 个

码元,每个码元周期10 ms[3]。

FPGA采集IRIG-B码并将除P码外89 个有效0或1

码元编码成4 个32 位SPI帧发送给ARM。FPGA发送AD

采样数据和编码后的IRIG-B码给ARM。同时FPGA将

GPS接受的PPS秒脉冲转发给ARM。另一路SPI中FPGA

从,ARM为主,用于接收ARM发送的控制信号,控制

AD采样的量程和电源。

FPGA在本设计中另外一个作用是,在GPS信号

丢失的情况下仍可为其他设备授时,FPGA采用外界

晶振模拟PPS秒脉冲并发送至ARM。在有GPS信号的

条件下,FPGA会对晶振每秒产生的时钟计数,实际

计数值可能与晶振理论频率值存在偏差记录偏差,

每10 s一个循环周期,计算循环周期内累加总偏差

值为T,求周期平均偏差T0=T/10[4]。当丢失GPS信

号后,FPGA将启用晶振结合T0来模拟精准度较高的

PPS秒脉冲为ARM授时。

3.2 底层驱动

串行外设接口SPI是一种高速的、全双工、同

步的通信总线[5]。本设计中FPGA与MP157使用SPI

总线传输协议完成数据传输,其中一路SPI中,

FPGA为主,MP157为从,因为是单主从结构,所以

SCLK、MOSI和CS片选三线可以完成数据传输任务。

因Linux开源代码中暂无ST芯片原厂的SPI从

机驱动,故需编写其驱动代码。将SPI从机驱动

建立在Platform虚拟总线平台上,实现驱动和设

备的分离。使用OF匹配表方式匹配设备和驱动,

匹配成功,执行probe函数。probe函数首先使用

spi_alloc_salve向内核申请SPI从机,然后通过

platform_get_resource函数从平台获取内存空间

作为SPI相关寄存器的映射,通过devm_ioremap_

resource函数返回这段内存的虚拟地址,程序通过

虚拟地址访问寄存器。虚拟地址和物理地址之间的

转换是通过MMU来完成[6]。接着对SPI寄存器进行初

始化,设置SPI一帧为32 位,CPOL和CPHA均为0,通

信方式为只接收,片选设置为SS PAD输入决定,硬

件片选。不使用片选进行时钟和数据同步会导致数

据移位问题。

FPGA与MP157通过SPI总线传输大量数据,使用

DMA传输减轻CPU负担。为避免出现cache与内存数

据不一致的问题,使用一致性DMA映射方式。使用

dma_alloc_cohernet函数申请DMA缓冲区,然后进

行DMA参数配置。dmaengine_perp_dma_cyclic绑定

回调函数。之后启动DMA的异步传输,等待数据到

来。另一路SPI,ARM作为主机,FPGA作为从机接收

控制信号。向Linux 内核注册成功spi_driver 以

后就可以使用SPI 核心层提供的API 函数来对设备

进行读写操作了。

3.3 业务驱动

MP157通过SPI总线从FGPA得到三通道原始数

据和IRIG-B码,数据量到达DMA缓冲区一半时,启

用DMA回调函数,在回调函数中启用tasklet中断下

半部中处理数据。接收到的三个通道的4 000Hz原

始数据放在三个环形缓冲队列,存放过去10 s钟的

数据。解析IRIG-B码可以得到当前的年、月、日、

时、分、秒等时间信息,计算出时间戳[7]。同时

FPGA会向MP157转发GPS模块的PPS秒脉冲信号,结

合解析的时间信息为数据打上时间标签。

在边缘端设备对原始数据进行FIR级联滤波降

采样处理,压缩数据量,降低网络频带要求。由于

滤波采用的是级联结构,减少资源的使用和计算

量,只设置2倍和5倍降采样滤波器,阶数分别为

N=72和N=24,从4 000 Hz先2倍降采样到2 000 Hz,

再5倍降采样到400 Hz,直到50 Hz,共5级。FIR软

件滤波器框图如图3所示。

原始数据和每一级的滤波数据均由环形缓冲区

存储,每一级保留10 s内数据,分为10个数据块,

如4 kHz原始数据的缓冲区偏移地址为0~4 000范

围内存放时间戳为1704377760s的采集数据,经过

滤波器2倍下采样将数据存放在2 kHz缓冲区偏移地

址为0~2 000范围内,每一级如此。当需要读取某

一分辨率的指定绝对秒时间内的数据的起始地址,

只需要找到绝对秒时间在原始数据缓冲区中块号即

可。采样率越低的数据,由于经过级数多,存在

数据延迟产生的问题。本设计使用多线程协同的

方式解决问题,它的核心思想是让每一级滤波用

kthread_create分配一个内核线程,每个线程分配

合理的时间,设定时间内即使没有完成新数据的滤

波工作,仍结束此次调度,进入等待队列,开始处

理下一级滤波器的滤波内核线程。

在应用程序和驱动交互中,驱动程序抽象为设

备文件的形式,在Linux下通过udev来实现设备文

件的创建与删除,应用程序对/dev目录下的设备文

件与驱动程序交互。业务驱动定义并实现其file_

operation结构体,ioctl接口传递采样设置参

数,定义lseek接口的whence参数设置缓冲区读指

针,read接口定义参数length读取样点数,并通过

copy_to_user返回给应用程序相应数据。

3.4 Linux应用程序

Linux应用程序使用C语言编写,驱动层设备文

件通过系统调用,每200 ms非阻塞的方式获取最新

数据,存储到外接的EMMC中,存放200 天的数据,

Linux操作系统提供相应的EMMC设备驱动和文件系

统方便用户对EMMC做读写操作。SSH服务可以让远

程客户端与开发板建立网络连接进行数据交互。

3.5 客户端软件

远程客户端采用有固定IP地址的PC机,用户交

互界面使用PyQt5平台实现。主要负责波形显示,也

可以向数据采集器下达控制指令,如采样率设置,

ADC量程设置,远程触发采集设置,以及电路电源,

通道开关功能。

4 结语

本文介绍了基于FPGA+ARM的地震数据采集器软

件设计方案。介绍FPGA软件、底层硬件驱动、业务

层驱动、Linux应用层到客户端一整套的软件设计逻

辑,系统实现数据从采集、处理、传输到显示,研

究成果对数据采集软件设计具有一定参考价值。